## Features

- Compliant with IEEE 802.3z Gigabit Ethernet

- Industry standard 2×5 footprint

- SC connector

- Single power supply 3.3 V

- Differential LVPECL inputs and outputs

- Compatible with solder and aqueous wash processes

- Class 1 laser product complies with EN 60825-1

- RoHS compliant

## **Ordering Information**

| PART NUMBER       | ТХ      | RX      | IN/OUT | SD     | TEMPERATURE                     | LD TYPE |

|-------------------|---------|---------|--------|--------|---------------------------------|---------|

| LSE2-C3U-PC-N5-BB | 1550 nm | 1310 nm | DC/DC  | LVPECL | $0^{\circ}$ C to $70^{\circ}$ C | DFB     |

| LSE2-C3U-TC-N5-BB | 1550 nm | 1310 nm | AC/AC  | LVTTL  | $0^{\circ}$ C to $70^{\circ}$ C | DFB     |

| LSE2-C3U-PI-N5-BB | 1550 nm | 1310 nm | DC/DC  | LVPECL | -40 °C to $85$ °C               | DFB     |

| LSE2-C3U-TI-N5-BB | 1550 nm | 1310 nm | AC/AC  | LVTTL  | -40 °C to $85$ °C               | DFB     |

## Absolute Maximum Ratings

| PARAMETER             | SYMBOL     | MIN  | MAX | UNITS | NOTE                |

|-----------------------|------------|------|-----|-------|---------------------|

| Storage Temperature   | $T_S$      | -40  | 85  | °C    |                     |

| Supply Voltage        | Vcc        | -0.5 | 4.0 | V     |                     |

| Input Voltage         | $V_{IN}$   | -0.5 | Vcc | V     |                     |

| Soldering Temperature | $T_{SOLD}$ |      | 260 | °C    | 10 seconds on leads |

## **Operating Environment**

| PARAMETER                   | SYMBOL            | MIN | MAX | UNITS | NOTE |

|-----------------------------|-------------------|-----|-----|-------|------|

| Constructions Transcrutture | Т                 | 0   | 70  | °C    |      |

| Case Operating Temperature  | $T_C$ -           | -40 | 85  | °C    |      |

| Supply Voltage              | Vcc               | 3.1 | 3.5 | V     |      |

| Supply Current              | $I_{TX} + I_{RX}$ |     | 350 | mA    |      |

# **Transmitter Electro-optical Characteristics** $Vcc = 3.1 \text{ V to } 3.5 \text{ V}, \text{ } \text{T}_{\text{C}} = 0 \text{ }^{\circ}\text{C} \text{ to } 70 \text{ }^{\circ}\text{C} (-40 \text{ }^{\circ}\text{C} \text{ to } 85 \text{ }^{\circ}\text{C})$

| PARAMETER                                      | SYMBOL                        | MIN  | TYP.    | MAX           | UNITS  | NOTE       |

|------------------------------------------------|-------------------------------|------|---------|---------------|--------|------------|

| Data Rate                                      | В                             |      | 1250    | 1300          | Mb/s   |            |

| Output Optical Power<br>9/125 μm fiber         | Pout                          | -2   |         | +3            | dBm    | Average    |

| Extinction Ratio                               | ER                            | 9    |         |               | dB     |            |

| Center Wavelength                              | $\lambda_C$                   | 1530 | 1550    | 1570          | nm     |            |

| Spectral Width (-20dB)                         | $\Delta\lambda$               |      |         | 1             | nm     |            |

| Side Mode Suppression Ratio                    | SMSR                          | 30   |         |               | dB     |            |

| Rise/Fall Time (10–90%)                        | T <sub>r</sub> , <sub>f</sub> |      |         | 260           | ps     |            |

| Output Eye                                     |                               |      | Complia | ant with IEEE | 802.3z |            |

| Output power when Disabled                     | $P_{OFF}$                     |      |         | -45           | dBm    | Average    |

| TX Disable Voltage-High                        |                               | 2    |         |               | V      | LVTTL      |

| TX Disable Voltage-Low                         |                               |      |         | 0.8           | V      | LVTTL      |

| Transmitter Data Input Voltage-High            | $V_{IH} - V_{CC}$             | -1.1 |         | -0.74         | V      |            |

| Transmitter Data Input Voltage-Low             | $V_{IL} - V_{CC}$             | -2.0 |         | -1.58         | V      |            |

| Transmitter Data Input Differential<br>Voltage | V <sub>DIFF</sub>             | 0.4  |         | 2.0           | V      | AC Coupled |

## **Receiver Electro-optical Characteristics** $Vcc = 3.1 \text{ V to } 3.5 \text{ V}, \text{ T}_{\text{C}} = 0 \text{ }^{\circ}\text{C} \text{ to } 70 \text{ }^{\circ}\text{C} (-40 \text{ }^{\circ}\text{C} \text{ to } 85 \text{ }^{\circ}\text{C})$

| PARAMETER                                    | SYMBOL            | MIN  | TYP. | MAX             | UNITS | NOTE             |

|----------------------------------------------|-------------------|------|------|-----------------|-------|------------------|

| Data Rate                                    | В                 |      | 1250 | 1300            | Mb/s  |                  |

| Optical Input Power-maximum                  | $P_{IN}$          | 0    |      |                 | dBm   | $BER < 10^{-12}$ |

| Optical Input Power-minimum<br>(Sensitivity) | P <sub>IN</sub>   |      |      | -25             | dBm   | $BER < 10^{-12}$ |

| Operating Center Wavelength                  | $\lambda_C$       | 1260 |      | 1360            | nm    |                  |

| Optical isolation                            | ISO               |      |      | -40             | dB    | λ=1480~1600nm    |

| Return Loss                                  | RL                |      |      | -14             | dB    | λ=1260~1360nm    |

| Signal Detect-Asserted                       | $P_A$             |      |      | -25             | dBm   | Average          |

| Signal Detect-Deasserted                     | $P_D$             | -40  |      |                 | dBm   | Average          |

| Signal Detect-Hysteresis                     | $P_A - P_D$       | 1.0  |      |                 | dB    |                  |

| Data Output Rise, Fall Time (20–80%)         | $T_{r,f}$         |      |      | 0.35            | ns    |                  |

| Signal Detect Output voltage-High            | $V_{OH} - V_{CC}$ | -1.1 |      | -0.74           | V     | LVPECL           |

| Signal Detect Output voltage-Low             | $V_{OL} - V_{CC}$ | -2.0 |      | -1.58           | V     | LVPECL           |

| Signal Detect Output voltage-High            | $V_{OH}$          | 2.4  |      | V <sub>CC</sub> | V     | LVTTL            |

| Signal Detect Output voltage-Low             | $V_{OL}$          | 0    |      | 0.4             | V     | LVTTL            |

| Data Output Voltage-High                     | $V_{OH} - V_{CC}$ | -1.1 |      | -0.74           | V     | LVPECL           |

| Data Output Voltage-Low                      | $V_{OL} - V_{CC}$ | -2.0 |      | -1.58           | V     | LVPECL           |

| Data Differential Output Voltage             | $V_{DIFF}$        | 0.6  |      | 1.8             | V     | AC Coupled       |

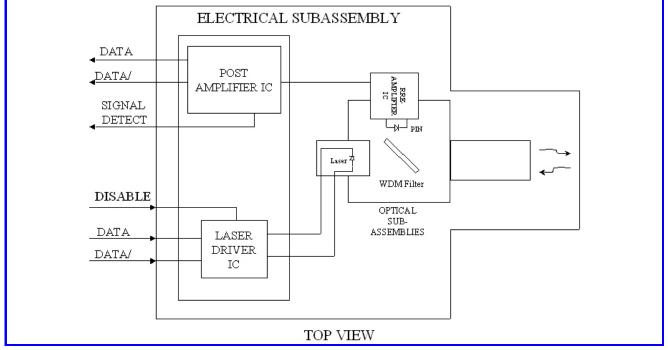

#### **Block Diagram of Transceiver**

#### Transmitter and Receiver Optical Sub-assembly Section

A 1550 nm InGaAsP laser and an InGaAs PIN photodiode integrate with an WDM filter to form a bi-directional single fiber optical subassembly (OSA). The laser of OSA is driven by a LD driver IC which converts differential input LVPECL logic signals into an analog laser driving current. And, The photodiode of OSA is connected to a circuit providing post-amplification quantization, and optical signal detection.

#### **Transmitter Disable**

Transmitter Disable is a LVTTL control pin. To disable the module, connect this pin to +3.3 V LVTTL logic high "1". While, to enable module connect to LVTTL logic low "0".

#### **Receiver Signal Detect**

Signal Detect is a basic fiber failure indicator. This is a single-ended LVPECL/LVTTL output. As the input optical power is decreased, Signal Detect will switch from high to low (deassert point) somewhere between sensitivity and the no light input level. As the input optical power is increased from very low levels, Signal Detect will switch back from low to high (assert point). The assert level will be at least 1.0 dB higher than the deassert level.

Page 5 of 12 Version 1.0 Date:05/31/2009

## **Connection Diagram**

Pin-Out

| PIN | SYMBOL            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RX GND            | Receiver Signal Ground, Directly connect this pin to the receiver ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2   | V <sub>CCR</sub>  | Receiver Power Supply<br>Provide +3.3 Vdc via the recommended receiver power supply filter circuit. Locate the power supply filter circuit as close as possible to the $V_{CCR}$ pin.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | SD                | Signal Detect.<br>Normal optical input levels to the receiver result in a logic "1" output, $V_{OH}$ , asserted. Low input optical levels<br>to the receiver result in a fault condition indicated by a logic "0" output $V_{OL}$ , deasserted Signal Detect is a<br>single-ended LVPECL output. <i>SD</i> can be terminated with LVPECL techniques via 50 $\Omega$ to $V_{CCR} - 2$ V.<br>Alternatively, <i>SD</i> can be loaded with a 180 $\Omega$ resistor to <i>RX GND</i> to conserve electrical power with small<br>compromise to signal quality. If Signal Detect output is not used, leave it open-circuited. |

| 4   | RD-               | <i>RD</i> – is an open-emitter output circuit.<br>Terminate this high-speed differential LVPECL output with standard LVPECL techniques at the follow-on device input pin. (See recommended circuit schematic)                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | RD+               | <i>RD</i> + is an open-emitter output circuit.<br>Terminate this high-speed differential LVPECL output with standard LVPECL techniques at the follow-on device input pin. (See recommended circuit schematic)                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | V <sub>CCT</sub>  | Transmitter Power Supply<br>Provide +3.3 Vdc via the recommended transmitter power supply filter circuit. Locate the power supply filter circuit as close as possible to the $V_{CCT}$ pin.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | TX GND            | Transmitter Signal Ground<br>Directly connect this pin to the transmitter signal ground plane. Directly connect this pin to the transmitter<br>ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8   | TX <sub>DIS</sub> | Transmitter Disable<br>Connect this pin to +3.3V LVTTL logic high "1" to disable transmitter. To enable module connect to<br>LVTTL logic low "0" or open.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9   | TD+               | Transmitter Data In<br>Terminate this high-speed differential LVPECL input with standard LVPECL techniques at the transmitter<br>input pin. (See recommended circuit schematic)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10  | TD–               | Transmitter Data In-Bar<br>Terminate this high-speed differential LVPECL input with standard LVPECL techniques at the transmitter<br>input pin. (See recommended circuit schematic)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Page 6 of 12 Version 1.0 Date:05/31/2009 Website: <u>www.apacoe.com.tw</u>

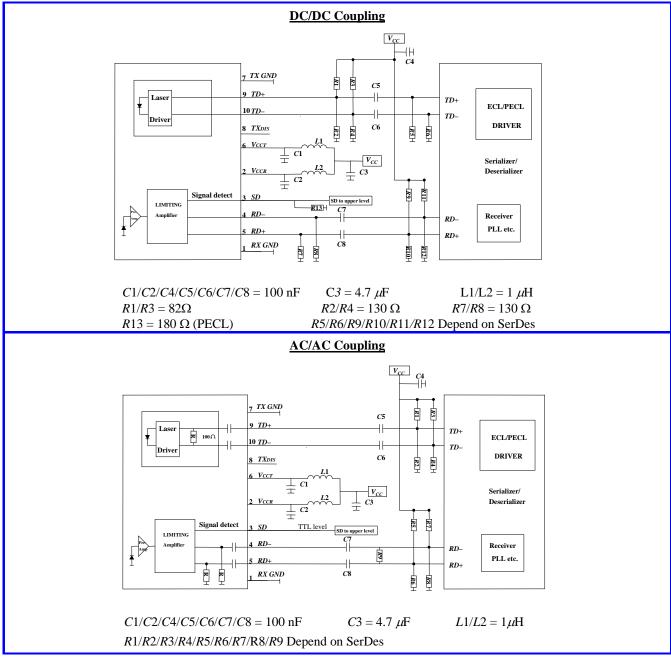

## Recommended Circuit Schematic

Page 7 of 12 Version 1.0 Date:05/31/2009

In order to get proper functionality, a recommended circuit is provided in above recommended circuit schematic. When designing the circuit interface, there are a few fundamental guidelines to follow.

- (1) The differential data lines should be treated as 50  $\Omega$  Micro strip or strip line transmission lines. This will help to minimize the parasitic inductance and capacitance effects. Locate termination at the received signal end of the transmission line. The length of these lines should be kept short and of equal length.

- (2) For the high speed signal lines, differential signals should be used, not single-ended signals, and these differential signals need to be loaded symmetrically to prevent unbalanced currents which will cause distortion in the signal.

- (3) Multi layer plane PCB is best for distribution of  $V_{CC}$ , returning ground currents, forming transmission lines and shielding, Also, it is important to suppress noise from influencing the fiber-optic transceiver performance, especially the receiver circuit.

- (4) A separate proper power supply filter circuits shown in Figure for the transmitter and receiver sections. These filter circuits suppress  $V_{CC}$  noise over a broad frequency range, this prevents receiver sensitivity degradation due to  $V_{CC}$  noise.

- (5) Surface-mount components are recommended. Use ceramic bypass capacitors for the 0.1  $\mu$ F capacitors and a surface-mount coil inductor for 1  $\mu$ H inductor. Ferrite beads can be used to replace the coil inductors when using quieter  $V_{CC}$  supplies, but a coil inductor is recommended over a ferrite bead. All power supply components need to be placed physically next to the  $V_{CC}$  pins of the receiver and transmitter.

- (6) Use a good, uniform ground plane with a minimum number of holes to provide a low-inductance ground current return for the power supply currents.

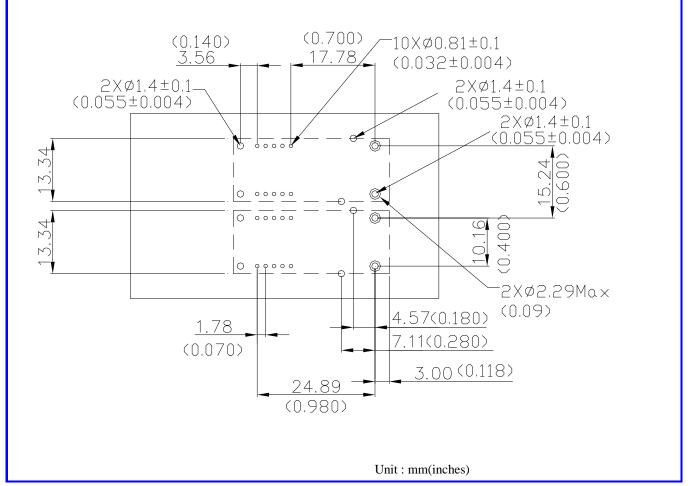

## **Recommended Board Layout Hole Pattern**

This transceiver is compatible with industry standard wave or hand solder processes. After wash process, all moisture must be completely remove from the module. The transceiver is supplied with a process plug to prevent contamination during wave solder and aqueous rinse as well as during handling, shipping or storage.

Solder fluxes should be water-soluble, organic solder fluxes. Recommended cleaning and degreasing chemicals for these transceivers are alcohol's (methyl, isopropyl, isobutyl), aliphatics (hexane, heptane) and other chemicals, such as soap solution or naphtha. Do not use partially halogenated hydrocarbons for cleaning/degreasing.

Page 9 of 12 Version 1.0 Date:05/31/2009

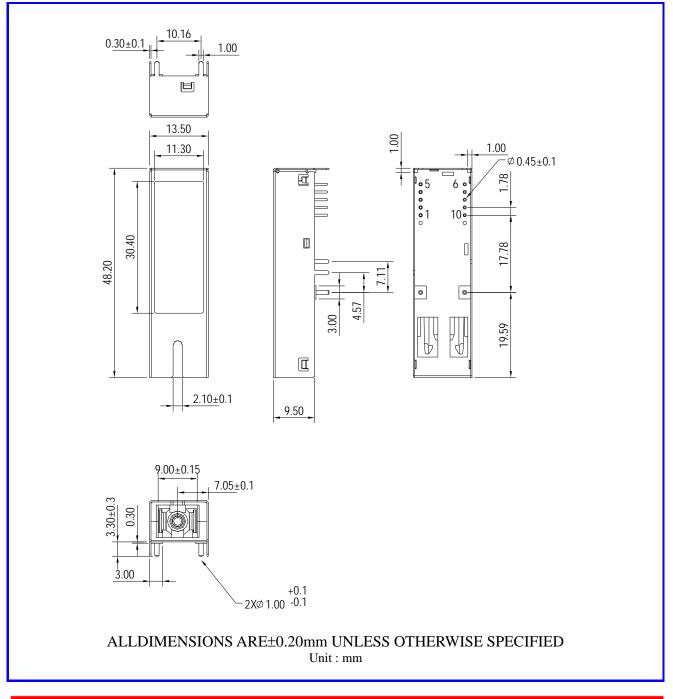

## **Drawing Dimensions**

Page 10 of 12 Version 1.0 Date:05/31/2009

## **Optical Receptacle Cleaning Recommendations**

All fiber stubs inside the receptacle portions were cleaned before shipment. In the event of contamination of the optical ports, the recommended cleaning process is the use of forced nitrogen. If contamination is thought to have remained, the optical ports can be cleaned using a NTT international Cletop® stick type and HFE7100 cleaning fluid. Before the mating of patchcord, the fiber end should be cleaned up by using Cletop® cleaning cassette.

Note: The pictures were extracted from NTT-ME website. And the Cletop® is a trademark registered by NTT-ME

## **Eye Safety Mark**

The LSE series Single mode transceiver is a class 1 laser product. It complies with EN 60825-1 and FDA 21 CFR 1040.10 and 1040.11. In order to meet laser safety requirements the transceiver shall be operated within the Absolute Maximum Ratings.

#### **Caution**

All adjustments have been done at the factory before the shipment of the devices. No maintenance and user serviceable part is required. Tampering with and modifying the performance of the device will result in voided product warranty.

## **Required Mark**

Class 1 Laser Product Complies with 21 CFR 1040.10 and 1040.11

Note : All information contained in this document is subject to change without notice.