#### **Features**

- Designed with Broadcom's BCM54210 chipset

- Complies with IEEE 802.3, 802.3u, and 802.3ab specifications

- Configured for operation with a SGMII compliant host

- Supports SyncE functionality (1000BASE-T connection only)

- Conforms to Multi-Source Agreement (MSA) specifications for SFP transceivers (Exceptions for SyncE features)

- Supports IEEE 802.3u and IEEE 802.3ab autonegotiation features to allow networking equipment to automatically determine and adjust the required settings

- Supports jumbo frames up to 18 KB

- Automatic MDI crossover, eliminating the need for crossover cables or cross-wired (MDIX) ports.

- Compact RJ45 connector assembly

- Detailed Product Information in EEPROM

- +3.3V Single Power Supply

- Access to Physical Layer IC and EEPROM via 2-wire serial bus (I2C)

- Compliant with RoHs

- Compliant with IEEE Std 802.3-2015

- Temperature range: -40°C to +85°C

### **Application**

- 10/100/1000Mbps Ethernet over Category 5/5e Cable

- Networking equipment

- High speed I/O for file server or high-end workstation

- Switch/Router to Switch/Router Link

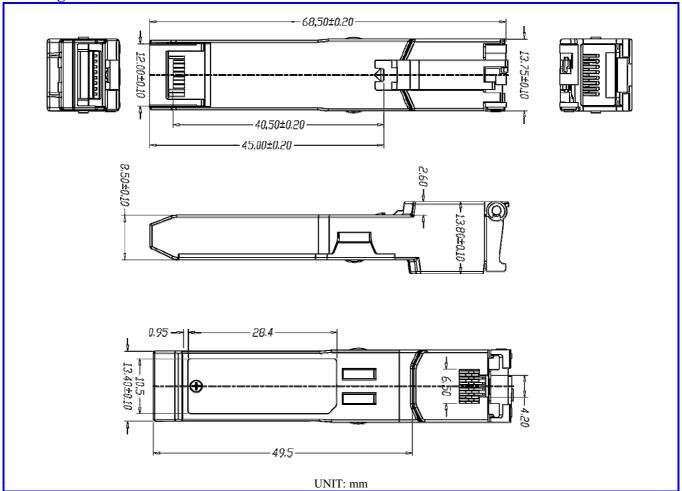

### **Description**

The 10/100/1000Base-T SFP Copper Transceiver named as ASFPT, which supports 1000Mb/s data-rate up to 100 meters reach over twisted-pair category 5/5e cable, is high performance and built-in MCU control with Synchronous Ethernet capability for SGMII host interface. The host interface transmits and receives serial data differentially at 1.25Gbps. The copper interface is advertised as full duplex and will auto-negotiate to 10/100/1000Base-T.

In addition, the ASFPT module provides standard serial ID information compliant with SFP MSA, which can be accessed with address of A0h via the 2-wire serial CMOS EEPROM protocol. The physical IC and SyncE feature controlled by register can also be accessed via 2-wire serial bus at address ACh and A2h, respectively.

Page 1 of 1 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

## **Ordering Information**

| PART NUMBER    | HOST INTERFACE     | Rx LOS               | SyncE                 | Auto-Negotiation | TEMPERATURE                        |

|----------------|--------------------|----------------------|-----------------------|------------------|------------------------------------|

| ASFPT-T3C-I-S0 | SGMII <sup>1</sup> | Enabled <sup>2</sup> | Disabled <sup>3</sup> | Yes              | $-40^{\circ}$ C to $+85^{\circ}$ C |

| ASFPT-T3C-S0   | SGMII              | Enabled              | Disabled              | Yes              | $0^{\circ}$ C to $+70^{\circ}$ C   |

#### **Notes:**

## **Absolute Maximum Ratings**

| PARAMETER           | SYMBOL | MIN | MAX | UNITS | NOTE    |

|---------------------|--------|-----|-----|-------|---------|

| Storage Temperature | $T_S$  | -40 | 90  | °C    | Ambient |

| Storage Humidity    | $H_S$  | 5   | 95  | %     |         |

## **Recommended Operating Conditions**

| PARAMETER                    | SYMBOL   | MIN  | TYP. | MAX  | UNITS | NOTE       |

|------------------------------|----------|------|------|------|-------|------------|

| Operating Temperature (Case) | $T_{I}$  | -40  | -    | 85   | °C    | Industrial |

| Operating Temperature (Case) | $T_C$    | 0    | -    | 70   | °C    | Commercial |

| Operating Humidity           | Но       | 10   | -    | 85   | %     |            |

| Supply Voltage               | $V_{CC}$ | 3.14 | 3.3  | 3.47 | V     |            |

| Supply Current               | $I_{CC}$ | -    | 245  | -    | mA    | 1000BASE-T |

### **General Specifications**

| PARAMETER        | SYMBOL              | MIN | TYP. | MAX | UNITS | NOTE              |

|------------------|---------------------|-----|------|-----|-------|-------------------|

| Distance         | $C_L$               | -   | -    | 100 | m     | Category 5/5e UTP |

| Line Frequency   | $F_{\mathit{Line}}$ |     | 25   | -   | MHz   |                   |

| RMS Phase Jitter | $F_J$               | -   | -    | 3   | psRMS | 1                 |

#### Note:

## **SyncE Specifications**

| PARAMETER               | SYMBOL | MIN | TYP. | MAX | UNITS | NOTE   |

|-------------------------|--------|-----|------|-----|-------|--------|

| Recovered Clock Jitter  |        | -50 | ±25  | 50  | ppm   |        |

| Recovered Clock         | RCO    | -   | 25   | -   | MHz   | 1      |

| Primary Reference Clock | PRC    | -   | 25   |     | MHz   | ±25ppm |

### Note:

1) 25 MHz for locally generated clock.

Page 2 of 2 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

<sup>&</sup>lt;sup>1</sup>SGMII is a mode of communication between MAC and PHY to allow for 10/100/1000BASE-T operation. If using GBIC mode, refer to the method of Appendix section D.

<sup>&</sup>lt;sup>2</sup>RxLOS is always enabled.

<sup>&</sup>lt;sup>3</sup>SyncE is defaulted as disabled. Enable SyncE functionality to refer Appendix section A, B, and E.

<sup>1)</sup>  $125MHz F_J = 12 kHz$  to 20 MHz offset frequency  $25MHz F_J = 1 kHz$  to 5 MHz offset frequency

## **Electrical Characteristics**

$V_{CC} = 3.3 \text{ V}, T = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}$

| PARAMETER                     | SYMBOL              | MIN           | TYP. | MAX                  | UNITS  | NOTE      |

|-------------------------------|---------------------|---------------|------|----------------------|--------|-----------|

| SGMII Receiver                |                     |               |      |                      |        |           |

| Baud rate                     | $R_{Baud}$          | -             | 1.25 | -                    | Gsym/s |           |

| Input differential threshold  | $V_{I,\ Diff}$      | 250           | =    | 1600                 | mVppd  | 1         |

| Differential Input Impedance  | $Z_{IN}$            | -             | 100  | -                    | Ω      |           |

| Disable Input-High            | $V_{DISH}$          | 2.0           | =    | V <sub>cc</sub> +0.3 | V      | 2         |

| Disable Input-Low             | $V_{\it DISL}$      | 0             | -    | 0.8                  | V      | 2         |

| SGMII Transmitter             |                     |               |      |                      |        |           |

| Output differential voltage   | $V_{O,\;Diff}$      | 600           | =    | 1200                 | mVppd  | 1         |

| Differential Output Impedance | $Z_{OUT}$           | -             | 100  | -                    | Ω      |           |

| Output Rise/Fall Time         | $T_R/T_F$           | 100           | -    | 200                  | ps     | 20% ~ 80% |

| Skew                          | $T_{\mathit{SKEW}}$ | -20           |      | 20                   | ps     | 3         |

| LOS Output Voltage – High     | Vsdhl               | $V_{cc}$ -0.4 | =    | V <sub>cc</sub> +0.3 | V      | 2         |

| LOS Output Voltage – Low      | $V_{SDL}$           | 0             | -    | 0.4                  | V      | 2         |

### Note:

- 1) Internally AC coupled, but requires a  $100\Omega$  differential termination.  $R_{load} = 100\Omega \pm 1\%$ .

- 2) Pull up to  $V_{\text{CC}}$  with a 4.7K to  $10 K\Omega$  resistors on the host board.

- 3) Skew between two members of a differential pair.

Page 3 of 3 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

### **LOS Function**

The SFP MSA specification defines a pin called LOS to indicate loss of signal to the motherboard. This should be pulled up with a 4.7K to 10K resistor. Pull up voltage between 2.0V and Vcc-T/R+0.3V. When high, this output indicates link fail. Low indicates normal operation. In the low state, the output will be pulled to <0.8V.

### **Termination Circuits**

Inputs to the transceiver are AC coupled and internally terminated through 50 Ohms. These modules can operate with PECL or ECL logic levels. The input signal must have at least a 250mV peak-to-peak (single ended) signal swing. Output from the receiver section of the module is also AC coupled and is expected to drive a 50 Ohms load. Different termination strategies may be required depending on the particular Serializer/Deserializer chip set used. The transceiver is designed with AC coupled data inputs and outputs to provide the following advantages:

Close positioning of SerDes with respect to transceiver; allows for shorter line lengths and at Gigabit speeds reduces EMI. It has minimum number of external components. Internal termination reduces the potential for un-terminated stubs which would otherwise increase jitter and reduce transmission margin.

Subsequently, this affords the customer the ability to optimally locate the SerDes as close to the transceiver as possible and save valuable real estate. At Gigabit rates this can provide a significant advantage resulting in better transmission performance and accordingly better signal integrity.

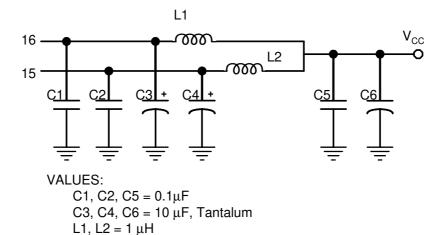

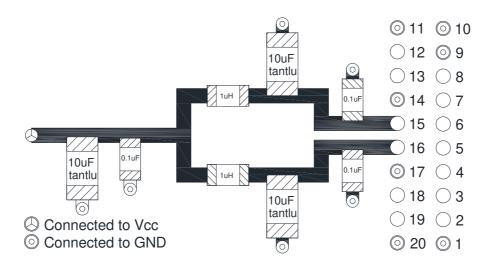

## **Power Coupling**

A suggested layout for power and ground connections is given in Figure 1 below. Connections are made via separate voltage and ground planes. The mounting posts are at case ground and should not be connected to circuit ground. The ferrite bead should provide a real impedance of 50 to 100 Ohms at 100 to 1000 MHz. Bypass capacitors should be placed as close to the 20 pin connector as possible.

Page 4 of 4 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303

TEL: +886-3-5986799 FAX: +886-3-5986655 Website: <u>www.apacoe.com.tw</u>

**Figure 1: Suggested Power Coupling**

### **Serial Communication Protocol**

The ASFPT module supports the 2-wire serial communication protocol defined in the SFP MSA and uses a 256-byte EEPROM with an address of A0h to store Table 1 data. The PHY IC and SyncE control register can also be accessed directly via the 2-wire serial bus at address ACh and A2h, respectively.

Page 5 of 5 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

## **EEPROM Serial ID Memory Contents**

Accessing Serial ID Memory uses the 2 wire address 10100000 (A0h). Memory Contents of Serial ID are shown in Table 1.

### **Table 1 Serial ID Memory Contents**

|        |                 | 14010                         | _ = = = = = = = = = = = = = = = = = = =                     |                                                                  |

|--------|-----------------|-------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|

| Addr.  | Size<br>(Bytes) | Name of Field                 | Hex                                                         | Description                                                      |

| 0      | 1               | identifier                    | 03                                                          | SFP or SFP+                                                      |

| 1      | 1               | Ext.Identifier                | 04                                                          | GBIC/SFP function is defined by two-wire interface ID only       |

| 2      | 1               | Connector                     | 22                                                          | RJ45                                                             |

| 3-10   | 8               | Transceiver                   | 00 00 00 08 00 00 00 00                                     | Transceiver Code                                                 |

| 11     | 1               | Encoding                      | 01                                                          | 8B/10B                                                           |

| 12     | 1               | BR(Nominal)                   | 0D                                                          | 1300Mbps                                                         |

| 13     | 1               | Rate Identifier               | 00                                                          | Unspecified                                                      |

| 14     | 1               | Length(SMFm)-km               | 00                                                          | N/A                                                              |

| 15     | 1               | Length(SMF)                   | 00                                                          | N/A                                                              |

| 16     | 1               | Length(50µm)                  | 00                                                          | N/A                                                              |

| 17     | 1               | Length(62.5μm)                | 00                                                          | N/A                                                              |

| 18     | 1               | Length(cable)                 | 64                                                          | 100(units of meters)                                             |

| 19     | 1               | Length(OM3)                   | 00                                                          | N/A                                                              |

| 20-35  | 16              | Vendor name                   | XX XX XX XX XX XX XX XX 20 20 20 20 20 20 20 20 20 20 20 20 | Vendor name (ASCII)                                              |

| 36     | 1               | Transceiver                   | 00                                                          | Unallocated                                                      |

| 37-39  | 3               | Vendor OUI                    | XX XX XX                                                    | Vendor OUI                                                       |

| 40-55  | 16              | Vendor PN                     | XX                      | Transceiver part number                                          |

| 56-59  | 4               | Vendor rev                    | XX XX XX XX                                                 | Vendor rev                                                       |

| 60-61  | 2               | Wavelength                    | 00                                                          | 0nm                                                              |

| 62     | 1               | Unallocated                   | 00                                                          | Unallocated                                                      |

| 63     | 1               | CC_BASE                       | Check Sum (Variable)                                        | Check code for Base ID Fields                                    |

| 64-65  | 2               | Options                       | 00 12                                                       | TX_Disable and LOS implemented                                   |

| 66     | 1               | BR                            | 00                                                          | max                                                              |

| 67     | 1               | BR                            | 00                                                          | min                                                              |

| 68-83  | 16              | Vendor SN                     | 41 34 32 30 33 30 30 34 20 20<br>20 20 20 20 20 20          | Serial Number of transceiver (ASCII).<br>For example "A4203004". |

| 84-91  | 8               | Date code                     | XX                               | Manufacture date code                                            |

| 92     | 1               | Diagnostic Monitoring<br>Type | 00                                                          | N/A                                                              |

| 93     | 1               | Enhanced Options              | 00                                                          | N/A                                                              |

| 94     | 1               | SFF-8472 Compliance           | 00                                                          | Digital diagnostic function not included or undefined            |

| 95     | 1               | CC_EXT                        | Check Sum (Variable)                                        | Check sum for Extended ID Field.                                 |

| 96-127 | 32              | Vendor Specific               | Read only                                                   | Depends on customer information                                  |

|        |                 |                               |                                                             |                                                                  |

**Note:** The "XX" byte should be filled in according to practical case. For more information, please refer to the related document of SFP Multi-Source Agreement (MSA).

Page 6 of 6 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799

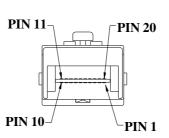

# **Connection Diagram**

Pin-Out

| Pin | Signal Name | Function                       | Descript                                               | Notes    |

|-----|-------------|--------------------------------|--------------------------------------------------------|----------|

| 1   | VeeT        | Transmitter Ground             | VeeT and VeeR are connected in SFP.                    | 7        |

|     | TX_FAULT    | Transmitter Fault Indication   | Not supported and Clock Output is disabled. (default)  | 1        |

| 2   | RCO         | Symphonous Ethomat Clash       | 125MHz clock locally generated                         | 8        |

|     | RCO         | Synchronous Ethernet Clock     | Recovered Clock                                        | 8, 9, 10 |

| 3   | TX_DISABLE  | Transmitter Disable            | Module disables on high or open                        | 2        |

| 4   | MOD DEF (2) | Module Definition 2            | Data Line (SDA) for Serial ID.                         | 3        |

| 5   | MOD DEF (1) | Module Definition 1            | Clock Line (SCL) for Serial ID.                        | 3        |

| 6   | MOD DEF (0) | Module Definition 0            | Grounded within the module                             | 3        |

| 7   | RATE SELECT | Not Implemented                | No connection required. (default)                      |          |

| /   | PRC         | Primary reference clock        | 25MHz frequency input                                  | 8, 10    |

| 8   | LOS         | Loss of Signal                 | See LOS option. (default)                              |          |

| 0   | PHY_INT     | PHY Interrupt                  | Logic '0' when PHY interrupt occurred, '1' otherwise   | 10       |

| 9   | VeeR        | Receiver Ground                | VeeT and VeeR are connected in SFP.                    | 7        |

| 10  | VeeR        | Receiver Ground                | VeeT and VeeR are connected in SFP.                    | 7        |

| 11  | VeeR        | Receiver Ground                | VeeT and VeeR are connected in SFP.                    | 7        |

| 12  | RD-         | Inverted Received Data out     | AC coupled 100 ohm differential high speed data lines. | 4        |

| 13  | RD+         | Non-Inverted Received Data out | AC coupled 100 ohm differential high speed data lines. | 4        |

| 14  | VeeR        | Receiver Ground                | VeeT and VeeR are connected in SFP.                    | 7        |

| 15  | VccR        | Receiver Power                 | VccR and VccT are connected in SFP.                    | 5        |

| 16  | VccT        | Transmitter Power              | VccR and VccT are connected in SFP.                    | 5        |

| 17  | VeeT        | Transmitter Ground             | VeeT and VeeR are connected in SFP.                    | 7        |

| 18  | TD+         | Non-inverted Data In           | AC coupled 100 ohm differential high speed data lines. | 6        |

| 19  | TD-         | Inverted Data In               | AC coupled 100 ohm differential high speed data lines  | 6        |

| 20  | VeeT        | Transmitter Ground             | Veet and VeeR are connected in SFP                     | 7        |

Page 7 of 7 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

#### **Notes:**

- 1. TX Fault is not used and is always tied to ground.

- TX disable is an input that is used to reset the chip of Gigabit Ethernet PHY inside the copper SFP. It is pulled up within the module with a 4.7-10 K Ohms resistor. Disable (PHY IC Disabled) >2V or open, Enable (PHY IC on) < 0.8V.

- Mod-Def 0, 1, 2 are the module definition pins. They should be pulled up with a 4.7-10K Ohms resistor on the host board to a supply between 2V and 3.6V.

- RD-/+: These are the differential receiver outputs. They are ac coupled 100 Ohms differential lines which should be terminated with 100 ohm differential at the user SerDes. The ac coupling is done inside the module and is thus not required on the host board. The voltage swing levels are compatible with CML and LVPECL voltage swings.

- VccR and VccT are the receiver and transmitter power supplies. They are defined as  $3.3 \text{ V} \pm 5\%$  at the SFP connector pin.

- TD-/+: These are the differential transmitter inputs. They are ac coupled differential lines with 100 Ohms differential termination inside the module. The ac coupling is done inside the module and is thus not required on the host board. The inputs levels are compatible with CML and LVPECL voltage swings.

- Circuit ground is connected to chassis ground.

- Clock output is enabled by set RCO Control flag in "SyncE Control" and recovered clock is enabled by "Recovered Clock Control".

- Recovery Clock:

- Link-down: 25 Mhz clock locally generated

- 1000BASE-T: 25Mhz clock recovered from line-side data

- 100BASE-TX: 25Mhz clock recovered from line-side data

- 10BASE-T: 2.5Mhz clock recovered from line-side data

- 10. PHY configuration also required.

Page 8 of 8 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799

### Mating of SFP Transceiver to SFP Host Board Connector

The pads on the PCB of the SFP transceiver shall be designed for a sequenced mating as follows: First mate: Ground contacts. Second mate: Power contacts. Third mate: Signal contacts The SFP MSA specification for a typical contact pad plating for the PCB is 0.38 micrometers minimum hard gold over 1.27 micrometers minimum thick nickel. To ensure the long term reliability performance after a minimum of 50 insertion removal cycles, the contact plating of the transceiver is 0.762 micro (30 micro-inches) over 3.81 micron (150 micro-inches) of Ni on Cu contact pads.

### **RJ45** Connector

RJ45 connector shall support shielded and unshielded cables. Also, the connector is mechanically robust enough and designed to prevent loss of link, when the cable is positioned or moves in different angles. The connector shall pass the "wiggle" RJ45 connector operational stress test. During the test, after the cable is plugged in, the cable is moved in circle to cover all 360 deg in the vertical plane, while the data traffic is on. There shall be no link or data loss.

Page 9 of 9 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799

## **Appendix:**

## A. SyncE Control Register (Default 0xBF)

| Bit | Name                | Description                                                                         | Default Value |

|-----|---------------------|-------------------------------------------------------------------------------------|---------------|

| 7   | Reserved            | Write 1 only                                                                        | 1             |

| 6   | Host Interface      | 1 = GBIC<br>0 = SGMII                                                               | 0             |

| 5   | Low Power Mode      | 1 = Low power mode released<br>0 = Low power mode active                            | 1             |

| 4   | PHY Reset Line      | 1 = PHY Reset line released<br>0 = PHY Reset line active                            | 1             |

| 3   | RCO Mode            | 1 = Normal RCO (2.5/25/125MHz)<br>0 = Restrict clock to 25MHz                       | 1             |

| 2   | RCO Control         | 1 = disable Clock Output (pin 2)<br>0 = enable Clock Output (pin 2)                 | 1             |

| 1   | LOS / PHY Interrupt | 1 = LOS functionality (pin 8)<br>0 = PHY Interrupt indication (pin 8)               | 1             |

| 0   | Clock Source Select | 1 = internal 25MHz Oscillator<br>0 = external Primary Reference Clock (pin 7) Input | 1             |

Note: direct access by write/read configuration byte to/from I2C device with any register address under A2h address.

#### **B. Recovered Clock Control**

| I2C Address | Control Register | Byte 1 | Byte 2 | Description                         |  |

|-------------|------------------|--------|--------|-------------------------------------|--|

| AC          | 17               | 0F     | 44     | Disable Pageward Cleak (default)    |  |

| AC          | 15               | 00     | 00     | - Disable Recovered Clock (default) |  |

| AC          | 17               | 0F     | 44     | Emphia Dagayarad Clasic             |  |

| AC          | 15               | 00     | 10     | - Enable Recovered Clock            |  |

Note: in HEX value

### C. Advertise 1000BASE-T full duplex capability and Master / Slave Configuration

| I2C Address | Control Register | Byte 1 | Byte 2 | Description                                    |

|-------------|------------------|--------|--------|------------------------------------------------|

| AC          | 09               | 02     | 00     | Automatic Master/Slave configuration (default) |

| AC          | 09               | 1A     | 00     | Configure SFP as Master                        |

| AC          | 09               | 12     | 00     | Configure SFP as Slave                         |

Note: in HEX value

Page 10 of 10 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799

## **D. Interface Selection**

At power up, the ASFPT module can be configured in GBIC or SGMII mode. The user may select a different host interface using one of the following methods:

### 1) Method 1

| I2C Address | Control Register | Byte 1 | Byte 2 | Description                 |

|-------------|------------------|--------|--------|-----------------------------|

| AC          | 1C               | FC     | FE     | Set mode to GBIC*           |

| AC          | 1C               | FC     | FC     | Set mode to SGMII (default) |

Note: in HEX value

### 2) Method 2

| I2C Address | <b>Configure Byte</b> | Description                                 |

|-------------|-----------------------|---------------------------------------------|

| A2          | EF                    | Set mode to GBIC mode PHY Reset line active |

| -           | -                     | Wait, at least 10 ms                        |

| A2          | FF                    | Release PHY Reset line                      |

| -           | -                     | Wait, at least 20 μs                        |

Note: in HEX value

## E. List of Supported IEEE Defined PHY Registers

| Register | Name                                  |

|----------|---------------------------------------|

| 00h      | Control                               |

| 01h      | Status                                |

| 02h-03h  | PHY Identification                    |

| 04h      | Auto-Negotiation Advertisement        |

| 05h      | Auto-Negotiation Link Partner Ability |

| 06h      | Auto-Negotiation Expansion            |

| 07h      | Next Page Transmit                    |

| 08h      | Link Partner Received Next Page       |

| 09h      | 1000Base-T Control                    |

| 0Ah      | 1000Base-T Status                     |

| 0Fh      | Extended Status                       |

| 19h      | Auxiliary Status Register             |

Page 11 of 11 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799

<sup>\*</sup>please also clear related Auto-Negotiation Advertisement bits in PHY Register 04h.

# 10/100/1000Base-T Copper Transceiver Supporting SyncE Small Form Pluggable (SFP), 3.3V

## 1) PHY Register 00h: Control

| Bit | Name                     | Description                                                     | R/W            | Default |

|-----|--------------------------|-----------------------------------------------------------------|----------------|---------|

|     |                          | Software Reset                                                  | R/W            |         |

| 15  | Reset                    | 1 = PHY reset                                                   | *Self-Clearing | 0       |

|     |                          | 0 = normal operation                                            | -Sen-Clearing  |         |

|     |                          | Internal loopback mode                                          |                |         |

| 14  | Loopback                 | 1 = enable loopback mode                                        | R/W            | 0       |

|     |                          | 0 = disable loopback mode                                       |                |         |

|     |                          | When auto-negotiation is disabled, bits 6 and 13 can be used to |                |         |

|     |                          | manually select the speed of operation Bits [6, 13]             |                |         |

| 13  | Speed Selection (LSB)    | 11 = Reserved                                                   | R/W            | 0       |

| 13  | Speed Selection (LSB)    | 10 = 1000 Mbps                                                  | IX/ VV         | U       |

|     |                          | 01 = 100 Mbps                                                   |                |         |

|     |                          | 00 = 10 Mbps                                                    |                |         |

|     |                          | If enabled, Auto-Negotiation result overrides Speed Selection,  |                |         |

| 10  | A Nanatiatian Earli      | Duplex Mode settings.                                           | R/W            | 1       |

| 12  | Auto-Negotiation Enable  | 1 = enable Auto-Negotiation process                             |                |         |

|     |                          | 0 = disable Auto-Negotiation process                            |                |         |

|     |                          | Placed SFP in a low-power mode. $1 = power down 0 = normal$     | D #11          | 0       |

| 11  | Power Down               | operation                                                       | R/W            |         |

| 10  |                          | 1 = isolate                                                     | D #11          | 0       |

| 10  | Isolate                  | 0 = normal operation                                            | R/W            | 0       |

|     |                          | When auto-negotiation is enabled, setting this bit restarts the |                |         |

|     |                          | Auto-Negotiation process.                                       | R/W            |         |

| 9   | Restart Auto-Negotiation | 1 = restart Auto-Negotiation process                            | *Self-Clearing | 0       |

|     |                          | 0 = normal operation                                            |                |         |

| 8   | Duplex Mode              | 1 = full duplex 0 = half duplex                                 | R/W            | 1       |

| 7   | Reserved                 | Write as 0, ignore on read                                      | R/W            | 0       |

| 6   | Speed Selection (MSB)    | Use in conjunction with bit 13                                  | R/W            | 1       |

| 5:0 | Reserved                 | Write as zero, ignore on read                                   | R/W            | 0x00    |

|     |                          |                                                                 |                |         |

## 2) PHY Register 01h: Status (default 0x7949)

| Bit | Name                   | Description                                                                                                                                 | R/W | Default |

|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|

| 15  | 100BASE-T4             | 100BASE-T4 protocol is not supported.  0 = not capable to perform 100BASE-T4                                                                | RO  | 0       |

| 14  | 100BASE-TX Full Duplex | 1 = capable to perform full duplex 100BASE-TX<br>0 = not capable to perform full duplex 100BASE-TX                                          | RO  | 1       |

| 13  | 100BASE-TX Half Duplex | 1 = capable to perform half duplex 100BASE-TX<br>0 = not capable to perform half duplex 100BASE-TX                                          | RO  | 1       |

| 12  | 10Base-T Full Duplex   | <ul><li>1 = capable to operate at 10Base-T in full duplex mode</li><li>0 = not capable to operate at 10Base-T in full duplex mode</li></ul> | RO  | 1       |

| 11  | 10Base-T Half Duplex   | <ul><li>1 = capable to operate at 10Base-T in half duplex mode</li><li>0 = not capable to operate at 10Base-T in half duplex mode</li></ul> | RO  | 1       |

| 10  | 100BASE-T2 Full Duplex | 100BASE-T2 protocol is not supported.  0 = not capable to perform full duplex 100BASE-T2                                                    | RO  | 0       |

| 9   | 100BASE-T2 Half Duplex | 100BASE-T2 protocol is not supported.  0 = not capable to perform half duplex 100BASE-T2                                                    | RO  | 0       |

| 8   | Extended Status        | 1 = extended status information in register 0x0Fh<br>0 = no extended status information in register 0x0Fh                                   | RO  | 1       |

Page 12 of 12 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

| 7 | Reserved                  | Ignore on read                                      | RO   | 0        |

|---|---------------------------|-----------------------------------------------------|------|----------|

|   |                           | 1 = PHY will accept management frames with preamble |      |          |

| 6 | 6 MF Preamble Suppression | suppressed                                          | RO   | 1        |

|   |                           | 0 = PHY  will not                                   |      |          |

| 5 | Auto-Negotiation Complete | 1 = Auto-Negotiation process completed              | D.O. | 0        |

| 3 |                           | 0 = Auto-Negotiation process not completed          | RO   | <u> </u> |

| 4 | Remote Fault              | 1 = remote fault condition detected                 | RO   | 0        |

| 4 |                           | 0 = no remote fault condition detected              | KO   | 0        |

| 3 | Auto-Negotiation Ability  | 1 = capable to perform Auto-Negotiation             | RO   | 1        |

| 2 | I in In Continu           | 1 = link is up                                      | RO   | 0        |

| 2 | Link Status               | 0 = link is down                                    | RO   | 0        |

| 1 | Jabber Detect             | 1 = jabber condition detected                       | RO   | 0        |

| 1 | Jabber Delect             | 0 = no jabber condition detected                    | KU   | U        |

| 0 | Extanded Canability       | 1 = extended register capabilities                  | RO   | 1        |

| U | Extended Capability       | 0 = basic register set capabilities only            | NO   | 1        |

## 3) PHY Register 02h-03h: PHY Identifier

| Bit   | Name                            | Description                                | R/W | Default |

|-------|---------------------------------|--------------------------------------------|-----|---------|

| 15:0  | Address 02h: PHY ID (MSB)       | MSB of PHY Identifier                      | RO  | 0x600D  |

| 15:10 | Address 03h: PHY ID (LSB) – OUI | LSB of PHY Identifier (* - PHY Rev Number) | RO  |         |

| 9:4   | Address 03h: Model              | Device model number                        |     | 0x859n  |

| 3:0   | Address 03h: Revision           | Device revision number                     |     |         |

Note that the n is the revision number. In the B0 version of the BCM54210, the read value of register 03h is 8599h.

### 4) PHY Register 04h: Auto-Negotiation Advertisement (default 0x01E1)

| Bit | Name                           | Description                                                                                             | R/W | Default |

|-----|--------------------------------|---------------------------------------------------------------------------------------------------------|-----|---------|

| 15  | Next Page                      | <ul><li>1 = Next Page capable</li><li>0 = no Next Page capability</li></ul>                             | R/W | 0       |

| 14  | Reserved                       | Write as zero, ignore on read                                                                           | R/W | 0       |

| 13  | Remote Fault                   | <ul><li>1 = remote fault supported</li><li>0 = no remote fault</li></ul>                                | R/W | 0       |

| 12  | Reserved                       | Write as zero, ignore on read                                                                           | R/W | 0       |

| 11  | Asymmetric Pause               | <ul><li>1 = advertise asymmetric pause</li><li>0 = advertise no asymmetric pause</li></ul>              | R/W | 0       |

| 10  | Pause Capable                  | <ul><li>1 = capable of full duplex pause operation</li><li>0 = not capable of pause operation</li></ul> | R/W | 0       |

| 9   | 100BASE-T4 Capable             | 100BASE-T4 protocol is not supported. Do not write 1. 0 = not capable to perform 100BASE-T4             | R/W | 0       |

| 8   | 100BASE TX Full Duplex Capable | 1 = 100BASE-TX full duplex capable<br>0 = Not 100BASE-TX full duplex capable                            | R/W | 1       |

| 7   | 100BASE-TX Half Duplex Capable | 1 = 100BASE-TX half duplex capable<br>0 = Not 100BASE-TX half duplex capable                            | R/W | 1       |

| 6   | 10BASE-T Full Duplex Capable   | 1 = 10BASE-T full duplex capable<br>0 = Not 10BASE-T full duplex capable                                | R/W | 1       |

| 5   | 10BASE-T Half Duplex Capable   | 1 = 10BASE-T half duplex capable<br>0 = Not 10BASE-T half duplex capable                                | R/W | 1       |

| 4:0 | Protocol Selector Field        | Selector Field mode: 00001 = IEEE 802.3 CSMA/CD.                                                        | R/W | 0x01    |

Page 13 of 13 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

5) PHY Register 05h: Auto-Negotiation Link Partner Ability (default 0x0000)

| Bit | Name                           | Description                                                                                                                 | R/W | Default |

|-----|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|---------|

| 15  | Next Page                      | <ul><li>1 = link partner capable of Next Page</li><li>0 = link partner not capable of Next Page</li></ul>                   | RO  | 0       |

| 14  | Acknowledge                    | <ul><li>1 = link partner has received link code word</li><li>0 = link partner has not received link code word</li></ul>     | RO  | 0       |

| 13  | Remote Fault                   | <ul><li>1 = link partner has detected remote fault</li><li>0 = link partner has not detected remote fault</li></ul>         | RO  | 0       |

| 12  | Reserved                       | Write as zero, ignore on read                                                                                               | RO  | 0       |

| 11  | Asymmetric Pause               | 1 = link partner wants asymmetric pause 0 = link partner does not want asymmetric pause                                     | RO  | 0       |

| 10  | 100BASE-T4 Capable             | <ul><li>1 = link partner is capable of pause operation</li><li>0 = link partner is not capable of pause operation</li></ul> | RO  | 0       |

| 9   | 100BASE-T4 Capable             | 1 = link partner is 100BASE-T4 capable<br>0 = link partner is not 100BASE-T4 capable                                        | RO  | 0       |

| 8   | 100BASE-TX Full Duplex Capable | 1 = link partner is 100BASE-TX full duplex capable<br>0 = link partner is not 100BASE-TX full duplex capable                | RO  | 0       |

| 7   | 100BASE-TX Half Duplex Capable | 1 = link partner is 100BASE-TX half duplex capable<br>0 = link partner is not 100BASE-TX half duplex capable                | RO  | 0       |

| 6   | 10BASE-T Full Duplex Capable   | 1 = Link partner is 10BASE-T full duplex capable<br>0 = Link partner is not 10BASE-T full duplex capable                    | RO  | 0       |

| 5   | 10BASE-T Half Duplex Capable   | 1 = link partner is 10BASE-T half duplex capable<br>0 = link partner is not 10BASE-T half duplex capable                    | RO  | 0       |

| 4:0 | Protocol Selector Field        | Link partner protocol selector field                                                                                        | RO  | 0x00    |

6) PHY Register 06h: Auto-Negotiation Expansion (default 0x0064)

| Bit  | Name                                   | Description                                                                                                                                                          | R/W | Default |

|------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|

| 15:7 | Reserved                               | Write as zero, ignore on read                                                                                                                                        | RO  | 0x00    |

| 6    | Receive Next Page Location Able        | <ul><li>1 = bit 5 determines Next Page receive location.</li><li>0 = bit 5 does not determine Next Page receive location</li></ul>                                   | RO  | 1       |

| 5    | Received Next Page Storage<br>Location | <ul><li>1 = link partner Next Pages are stored in Register 8</li><li>0 = link partner Next Pages are stored in Register 5</li></ul>                                  | RO  | 1       |

| 4    | Parallel Detection Fault               | <ul> <li>1 = a fault has been detected via the Parallel Detection function</li> <li>0 = a fault has not been detected via the Parallel Detection function</li> </ul> | RO  | 0       |

| 3    | Link Partner Next Page Able            | <ul><li>1 = link Partner is Next Page able</li><li>0 = link Partner is not Next Page able</li></ul>                                                                  | RO  | 0       |

| 2    | Next Page Able                         | <ul><li>1 = local Device is Next Page able</li><li>0 = local Device is not Next Page able</li></ul>                                                                  | RO  | 1       |

| 1    | Page Received                          | <ul><li>1 = a New Page has been received</li><li>0 = a New Page has not been received</li></ul>                                                                      | RO  | 0       |

| 0    | Link Partner Auto-Negotiation Able     | 1 = link Partner is Auto-Negotiation able 0 = link Partner is not Auto-Negotiation able                                                                              | RO  | 0       |

Page 14 of 14 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

## 7) PHY Register 07h: Next Page Transmit (default 0x2001)

| Bit  | Name                           | Description                                                                        | R/W | Default |

|------|--------------------------------|------------------------------------------------------------------------------------|-----|---------|

| 15   | Next Page                      | <ul><li>1 = additional Next Pages to follow</li><li>0 = last Next Page</li></ul>   | R/W | 0       |

| 14   | Reserved                       | Write as zero, ignore on read                                                      | RO  | 0       |

| 13   | Message Page                   | 1 = message page<br>0 = unformatted page                                           | R/W | 1       |

| 12   | Acknowledge 2                  | <ul><li>1 = complies with message</li><li>0 = cannot comply with message</li></ul> | R/W | 0       |

| 11   | Toggle1                        | Toggles between exchanges of different Next Pages                                  | RO  | 0       |

| 10:0 | Message/Unformatted Code field | Next Page message code or unformatted data                                         | R/W | 0x001   |

### 8) PHY Register 08h: Link Partner Received Next Page (default 0x0000)

| Bit  | Name               | Description                                                                        | R/W | Default |

|------|--------------------|------------------------------------------------------------------------------------|-----|---------|

| 15   | Next Page          | <ul><li>1 = additional Next Pages to follow</li><li>0 = last Next Page</li></ul>   | RO  | 0       |

| 14   | Acknowledge        | 1 = acknowledge<br>0 = no acknowledge                                              | RO  | 0       |

| 13   | Message Page       | 1 = message page<br>0 = unformatted page                                           | RO  | 0       |

| 12   | Acknowledge 2      | <ul><li>1 = complies with message</li><li>0 = cannot comply with message</li></ul> | RO  | 0       |

| 11   | Toggle2            | Toggles between exchanges of different Next Pages                                  | RO  | 0       |

| 10:0 | Message Code field | Next Page message code or unformatted data                                         | RO  | 0x000   |

## 9) PHY Register 09h: 1000Base-T Control (default 0x0200)

| Bit   | Name                              | Description                                                      | R/W    | Default |

|-------|-----------------------------------|------------------------------------------------------------------|--------|---------|

|       |                                   | 000 = normal operation                                           |        |         |

|       |                                   | 001 = test mode 1—Transmit waveform test                         |        |         |

| 15:13 | Test mode bits                    | 010 = test mode 2—Master transmit jitter test                    | R/W    | 0x0     |

| 13.13 |                                   | 011 = test mode 3—Slave transmit jitter test                     | IX/ VV | OAO     |

|       |                                   | 100 = test mode 4—Transmitter distortion test                    |        |         |

|       |                                   | 101, 110, 111 = reserved                                         |        |         |

| 12    | Master/Slave Manual Config Enable | 1 = manual Master/Slave configuration                            | R/W    | 0       |

| 12    | Master/Stave Manual Config Enable | 0 = automatic Master/Slave configuration                         |        | 0       |

| 11    | Master/Slave Config Value         | 1 = configure PHY as Master                                      | R/W    | 0       |

| 11    |                                   | 0 = configure PHY as Slave This bit is ignored if bit $12 = 0$ . |        |         |

| 10    | D 44                              | 1 = indicate the preference to operate as multiport device $0 =$ | R/W    | 0       |

| 10    | Port type                         | indicate the preference to operate as single-port device         | K/W    |         |

| 0     | 1000D A CE T E-11 D1              | 1 = advertise 1000BASE-T full duplex capability                  | R/W    |         |

| 9     | 1000BASE-T Full Duplex            | 0 = advertise no 1000BASE-T full duplex capability               |        | 1       |

| 0     | 100000 ACE THE ICO                | 1 = advertise 1000BASE-T half duplex capability                  | D/W/   | 0       |

| 8     | 1000BASE-T Half Duplex            | 0 = advertise no 1000BASE-T half duplex capability               | R/W    | 0       |

| 7:0   | Reserved                          | Write as 0, ignore on read                                       | R/W    | 0x00    |

Page 15 of 15 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799 FAX: +886-3-5986655

## 10) PHY Register 0Ah: 1000Base-T Status (default 0x0000)

| Bit | Name                                  | Description                                                                                                              | R/W | Default |

|-----|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|---------|

| 15  | Master/Slave configuration fault      | <ul><li>1 = Master/Slave configuration fault detected</li><li>0 = No Master/Slave configuration fault detected</li></ul> | RO  | 0       |

| 14  | Master/Slave configuration resolution | <ul><li>1 = Local transmitter is Master</li><li>0 = Local transmitter is Slave</li></ul>                                 | RO  | 0       |

| 13  | Local Receiver Status                 | 1 = Local receiver OK<br>0 = Local receiver not OK                                                                       | RO  | 0       |

| 12  | Remote Receiver Status                | 1 = Remote Receiver OK<br>0 = Remote Receiver not OK                                                                     | RO  | 0       |

| 11  | LP 1000T FD                           | 1 = Link partner is capable of 1000BASE-T full duplex 0 = Link partner is not capable of 1000BASE-T full duplex          | RO  | 0       |

| 10  | LP 1000T HD                           | 1 = Link partner is capable of 1000BASE-T half duplex<br>0 = Link partner is not capable of 1000BASE-T half duplex       | RO  | 0       |

| 9:8 | Reserved                              | Write as zero, ignore on read                                                                                            | RO  | 0x0     |

| 7:0 | Idle Error Count                      | Indicate the idle Error count, since last read                                                                           | RO  | 0x00    |

## 11) PHY Register 0Fh: Extended Status (default 0x3000)

| Bit  | Name                   | Description                                                                                                 | R/W | Default |

|------|------------------------|-------------------------------------------------------------------------------------------------------------|-----|---------|

| 15   | 1000BASE-X Full Duplex | tolex $1 = 1000 \text{BASE-X full duplex capable}$ $0 = \text{Not } 1000 \text{BASE-X full duplex capable}$ |     | 0       |

| 14   | 1000BASE-X Half Duplex | 1 = 1000BASE-X half duplex capable<br>0 = Not 1000BASE-X half duplex capable                                | RO  | 0       |

| 13   | 1000BASE-T Full Duplex | 1 = 1000BASE-T full duplex capable<br>0 = Not 1000BASE-T full duplex capable                                | RO  | 1       |

| 12   | 1000BASE-T Half Duplex | 1 = 1000BASE-T half duplex capable<br>0 = Not 1000BASE-T half duplex capable                                | RO  | 1       |

| 11:0 | Reserved               | Write as zero, ignore on read                                                                               | RO  | 0x000   |

## 12) PHY Register 19h: Auxiliary Status Register (default 0x0000)

| Bit   | Name                                                                                                                                                                                                                                                   | Description                                                                                                         |    | Default |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----|---------|--|

| 15    | Auto-Negotiation Complete                                                                                                                                                                                                                              | <ul><li>1 = Auto-Negotiation process completed</li><li>0 = Auto-Negotiation process not completed</li></ul>         | RO | 0       |  |

| 14:11 | Reserved                                                                                                                                                                                                                                               | Reserved.                                                                                                           | RO | 0x0     |  |

| 10:8  | 000 = Link has not been established 001 = 10BASE-T half-duplex 010 = 10BASE-T full-duplex Current Operating Speed and Duplex mode 011 = 100BASE-TX half-duplex 100 = 100BASE-TX full-duplex 110 = 1000BASE-TX full-duplex 111 = 1000BASE-T full-duplex |                                                                                                                     | RO | 0x0     |  |

| 7     | Parallel Detection Fault                                                                                                                                                                                                                               | <ul><li>1 = Parallel link fault detected</li><li>0 = Parallel link fault not detected</li></ul>                     | RO | 0       |  |

| 6     | Remote Fault                                                                                                                                                                                                                                           | <ul><li>1 = Link partner has detected remote fault</li><li>0 = Link partner has not detected remote fault</li></ul> | RO | 0       |  |

| 5     | Page Received                                                                                                                                                                                                                                          | 1 = New page has been received from link partner 0 = New page has not been received                                 | RO | 0       |  |

Page 16 of 16 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799

| 4 | Link Partner Auto-Negotiation  | 1 = Link partner has Auto-Negotiation capability    | RO   | 0 |

|---|--------------------------------|-----------------------------------------------------|------|---|

|   | Ability                        | 0 = Link partner does not perform Auto-Negotiation  | RO   | 0 |

| 2 | Link Partner Next Page Ability | 1 = Link partner has next Page capability           | RO   | 0 |

| 3 |                                | 0 = Link partner does not have Next Page capability | RO   | U |

| 2 | 11.1.0                         | 1 = Link status is OK                               | DO.  | 0 |

|   | Link Status                    | 0 = Link status is not OK                           | RO   | 0 |

| 1 | Pause Resolution RX            | 1 = Enable pause receive                            | D.O. | 0 |

| 1 |                                | 0 = Disable pause receive                           | RO   |   |

| 0 | Pause Resolution TX            | 1 = Enable pause transmit                           | D.O. |   |

|   |                                | 0 = Disable pause transmit                          | RO   | 0 |

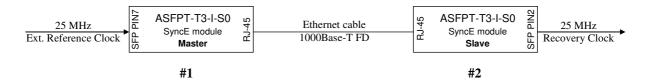

# F. SyncE Configuration Example

The recovered clock is 25MHz when the ASFPT module is linked in 1000BASE-T Slave modes. In 1000BASE-T mode, to output the recovery clock from the link partner, the ASFPT module must auto-negotiate to Slave mode. If the ASFPT module auto-negotiates to master mode, the ASFPT module would recover its own clock, not the clock of the link partner. 10BASE-T is Manchester encoder, and the clock phase information is only transmitted when a packet is being transmitted, so 10BASE-T cannot be used for Synchronous Ethernet.

#1 Enabled primary reference 25MHz clock input on pin 7 for the SFP in Master mode - SyncE Configuration Sequence

| I2C Address | Control Register/<br>Config. Byte | Byte 1 | Byte 2 | Description                                                  |

|-------------|-----------------------------------|--------|--------|--------------------------------------------------------------|

| A2          | FE                                | -      | -      | Enable external Primary Reference Clock Input (pin 7)        |

| AC          | 09                                | 1A     | 00     | Configure SFP as manual Master mode (1000BASE-T full duplex) |

| AC          | 00                                | 13     | 40     | Restart Auto-Negotiation                                     |

Note: in Hex value

#2 Enabled recovery clock output on pin 2 for the SFP in Slave mode - SyncE Configuration Sequence

| I2C Address | Control Register/ Config. Byte | Byte 1 | Byte 2 | Description                                                 |

|-------------|--------------------------------|--------|--------|-------------------------------------------------------------|

| AC          | 17                             | 0F     | 44     | - Enable Cleak Data Pagayary Process                        |

| AC          | 15                             | 00     | 10     | Enable Clock Data Recovery Process                          |

| A2          | BB                             | -      | -      | Enable Clock Output (pin 2)                                 |

| AC          | 09                             | 12     | 00     | Configure SFP as manual Slave mode (1000BASE-T full duplex) |

| AC          | 00                             | 13     | 40     | Restart Auto-Negotiation                                    |

Note: in Hex value

Page 17 of 17 Version 1.1 Date: 9/1/2021 Headquarters:

3 Tzu Chiang Road, Hsinchu Industrial Park, Hukow,

Hsinchu Hsien, Taiwan 303 TEL: +886-3-5986799