# UltraFast High-Level Productivity Design Methodology Guide

UG1197 (v2015.4) November 18, 2015

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                  |

|------------|---------|---------------------------|

| 11/18/2015 | 2015.4  | Initial document release. |

# **Table of Contents**

| Chapter 1: High-Level Productivity Design Methodology |  |  |  |  |                          |

|-------------------------------------------------------|--|--|--|--|--------------------------|

| About This Guide                                      |  |  |  |  |                          |

|                                                       |  |  |  |  | Chapter 2: System Design |

|                                                       |  |  |  |  | Overview                 |

|                                                       |  |  |  |  | System Partitioning      |

| System Development                                    |  |  |  |  |                          |

| Vivado IP Catalog                                     |  |  |  |  |                          |

| IP Integrator and Standard Interfaces                 |  |  |  |  |                          |

| Chapter 3: Platform Development                       |  |  |  |  |                          |

| Overview                                              |  |  |  |  |                          |

| Platform Design                                       |  |  |  |  |                          |

| Platform Verification                                 |  |  |  |  |                          |

| Chapter 4: C-Based IP Development                     |  |  |  |  |                          |

| Overview                                              |  |  |  |  |                          |

| Fast C Verification                                   |  |  |  |  |                          |

| C Language Support for Synthesis                      |  |  |  |  |                          |

| Using Hardware Optimized C Libraries                  |  |  |  |  |                          |

| Understanding Vivado HLS                              |  |  |  |  |                          |

| Optimization Methodology                              |  |  |  |  |                          |

| Optimization Strategies                               |  |  |  |  |                          |

| RTL Verification                                      |  |  |  |  |                          |

| IP Packaging                                          |  |  |  |  |                          |

| Design Analysis and Optimization 58                   |  |  |  |  |                          |

| Chapter 5: System Integration                         |  |  |  |  |                          |

| Overview                                              |  |  |  |  |                          |

| Initial System Integration                            |  |  |  |  |                          |

| Automated System Integration                       | 65         |

|----------------------------------------------------|------------|

| Designing for the Future                           | 68         |

| Appendix A: Additional Resources and Legal Notices |            |

| Xilinx Resources                                   | <b>7</b> 1 |

| Solution Centers                                   | <b>7</b> 1 |

| References                                         | <b>7</b> 1 |

| Training Resources                                 | 72         |

| Places Peads Important Logal Nations               | 7          |

# High-Level Productivity Design Methodology

# **About This Guide**

Xilinx® programmable devices have capacities of multi-million Logic Cells (LC), and integrate an ever-increasing share of today's complex electronic systems. This High-Level Productivity Design Methodology provides a set of best practices to create such complex systems within short design cycles.

The methodology focuses on the following concepts:

- Using parallel development flows for the valuable Intellectual Property (IP) which differentiates your products in the marketplace and the platform used to integrate your IP with the rest of the ecosystem.

- Extensive use of a C-based IP development flow to provide simulations that are orders

of magnitude faster than RTL simulations, as well as accurately timed and optimized

RTL.

- Use of existing pre-verified platform, block, and component-level IP to quickly build your system.

- Use of scripts to highly automate the flow from accurate design validation through to programmed FPGA.

The recommendations in this guide have been gathered from a large pool of expert users over the past few years. They have consistently delivered the following improvements over traditional RTL design methodologies:

- 4X speed up in development time for designs.

- 10X speed up in the development time for derivative designs.

- 0.7X to 1.2X the Quality of Results (QoR).

Although this guide focuses on large complex designs, the practices discussed are suitable for, and have successfully been applied in, all types of design including:

- Digital Signal Processing:

- Image processing

- Video

- Radar

- Automotive

- Processor acceleration

- Wireless

- Storage

- Control systems

# **Need for a New Design Methodology**

The advanced designs used in today's increasingly complex electronic products are stretching the boundaries of density, performance, and power. They create a challenge for design teams to hit a target release window within their allocated budget.

A productive methodology for addressing these design challenges is one where more time is spent at higher levels of abstraction, where verification times are the fastest and productivity gains are the greatest.

The need for a new design methodology is highlighted in the following figure, where the area of each region represents the percentage of development effort at each stage of the design flow.

- With a traditional RTL methodology most of the effort is spent on the implementation details

- In a high-level productivity design methodology, most of the effort is spent designing and verifying you are building the right system.

Algorithmic Design Methodology

# Platform & IP Reuse C Based IP Design Place & IP Configuration IP Integration Pesign Closure Place C Based IP Design Closure

#### Figure 1-1: High-Level Productivity Design Methodology Comparison

# **Traditional Methodology**

Traditional RTL Methodology

Traditional design development starts with experienced designers estimating how their design will be implemented in a new technology, capturing the design in Register Transfer Levels (RTLs), performing a few trials through synthesis and P&R to confirm their estimations and then proceeding to capture the remainder of the design. This is done while typically synthesizing each block in turn to re-confirm that the implementation details are acceptable.

The primary method for confirming that the design provides the intended functionality is to simulate the RTL. The detailed bit-accurate and cycle-accurate nature of an RTL description, although highly accurate, makes this process both slow and error prone.

Only when all blocks in the design have been captured in RTL can a full verification of the system be performed, often resulting in adjustments to the RTL. After all blocks in the system have been verified, they can be placed and routed together, and the accuracy of earlier estimations of timing and area can be either fully confirmed or shown to be inaccurate. This also often results in changes to the RTL, re-initiating another verification of the system and another re-implementation.

Designers are now often required to implement hundreds of thousands of lines of RTL code in a given project and spend much of their design time on implementation details. As highlighted in Figure 1-1, designers spend considerably more of their time implementing the design, rather than designing the novel and innovative solutions that all products require to remain competitive.

Moving to a newer technology to improve performance or a slower technology to provide more competitive pricing often means the majority of the RTL has to be re-written; designers must re-implement the amount of logic between the registers.

# **High-Level Productivity Design Methodology**

The High-Level Productivity Design Methodology traverses the same basic steps as a more traditional RTL methodology, as shown in Figure 1-1. However, it allows designers to spend more time designing value-add solutions. The main attributes of a high productivity methodology are:

- The concept of platform IP which captures the IO peripherals and interfaces in a separate design project which is developed and verified in parallel with the main design IP.

- Using C-based IP simulation to increase simulation times by orders of magnitude over traditional RTL simulation, providing designers the time to design the ideal solution.

- Using the Xilinx Vivado® Design Suite to highly automate the path to timing closure through the use of C-based IP development, IP re-use and standard interfaces.

- Making use of the Vivado IP Catalog to easily re-use your own platform, block and component level IP and provide easy access to the Xilinx IP already verified and known to implement well in the technology.

All steps in the High-Level Productivity Design Methodology can be performed interactively or using command line scripts. The result of all manual interactions can be saved to scripts, allowing the entire flow to be fully automated, from the design simulation through to programming the FPGA. Depending on your design and the runtime of the RTL system level simulation, this flow makes it possible to generate an FPGA bitstream and test the design on the board, often before any RTL design simulation has completed.

Even greater productivity improvements come when design derivatives are created. C-based IP is easily targeted to different devices, technologies, and clock speeds: as easy as changing a tool option. A fully scripted flow, with automated timing closure through C synthesis, means derivative designs can be quickly verified and assembled.

# **Design Process**

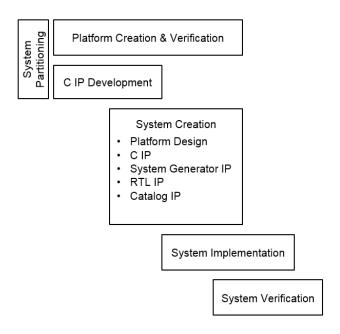

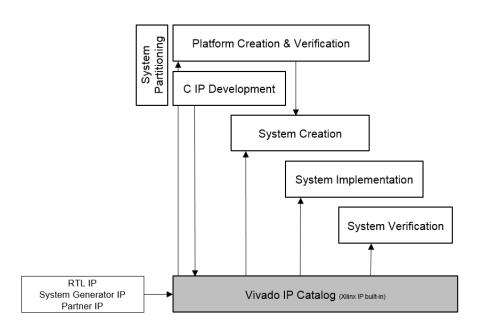

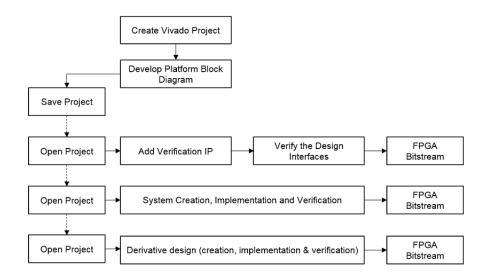

The steps in the design process are shown in the following figure.

Figure 1-2: High-Level Productivity Design Flow

After the initial stage of system partitioning, described in Chapter2, System Design. A key feature of this design flow is the overlapping nature of the development.

- A Platform Development Flow: Through the use of Vivado IP Integrator and the IP

Catalog, the Vivado Design Suite enables fast, efficient block-level integration. Much of

the critical aspects for system performance, including detail orientated interface

creation, verification, and pin-planning, can be separated into a parallel development

effort and given the focus they require. This flow is described in Chapter 3, Platform

Development.

- **C Based IP Development**: It takes approximately 1 or 2 days to simulate a full frame of video using RTL simulation (depending on the design, the host machine, etc.). It takes approximately 10 seconds to perform the same bit-level accurate simulation using C/C++. The productivity benefits of a C-based development flow cannot be ignored. This flow is described in Chapter 4, C-Based IP Development.

- **System Creation**: Vivado IP integrator and the IP catalog allow C-based IP to be quickly combined into a system block design using the platform design, legacy RTL IP, System Generator IP, and Xilinx IP. Automated interface connections and the ability to script the system creation mean that the system can be generated and re-generated

quickly throughout the IP development process. This flow is described in Chapter 5, System Integration.

- **System Implementation**: You can ensure that minimal time is spent on design closure by using a platform design that is already verified, C-based IP automatically optimized for the device and clock frequency, and existing verified IP, all connected through industry standard ARM AMBA® AXI4 protocol-compliant interfaces. This flow is launched from the system block design with a few clicks of the mouse or using a scripted flow. This flow is described in Chapter 5, System Integration.

- **System Verification**: This is be performed using gate-level accurate RTL simulations and/or by programing the FPGA and verifying the design on the board. Because the RTL simulations are used to verify the system—not the iterative simulations used to validate and design during development—only a single simulation is required at the end of the design flow. This flow is described in Chapter 5, System Integration.

# **Accessing Documentation and Training**

Access to the right information at the right time is critical for timely design closure and overall design success. Reference guides, user guides, tutorials, and videos get you up to speed as quickly as possible with the Vivado Design Suite. This section lists some of the sources for documentation and training.

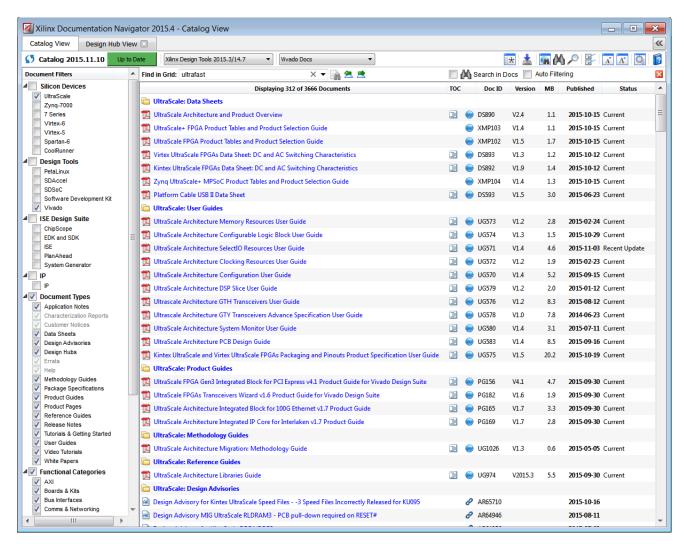

# **Using the Documentation Navigator**

The Vivado Design Suite ships with the Xilinx Documentation Navigator, as shown in Figure 1-3, page 11, which provides an environment to access and manage the entire set of Xilinx software and hardware documentation, training, and support materials. The Documentation Navigator allows you to view current and past Xilinx documentation. You can filter the documentation display based on release, document type, or design task. When coupled with a search capability, you can quickly find the right information. Methodology Guides appear as one of the filters under Document Types, which allows you to reach any of Methodology Guides almost instantaneously.

Xilinx uses the Documentation Navigator to provide you with up-to-date documentation using the Update Catalog feature. This feature alerts you about available catalog updates and provides details about the documents that are involved. Xilinx recommends that you always update the catalog when alerted to keep it current. Additionally, you can establish and manage local documentation catalogs with specified documents.

The Documentation Navigator has a tab called the **Design Hub View**. Design hubs are collections of documentation related by design activity, such as Applying Design Constraints, Synthesis, Implementation, and Programming and Debug. Documents and videos are organized in each hub in order to simplify the learning curve for that area. Each hub contains sections such as Getting Started, Support Resources (with an FAQ for that

flow), and Additional Learning Materials. For new users, the Getting Started section provides a good place to start. For those already familiar with the flow, Key Concepts and the FAQ may be of particular interest to gain expertise with the Vivado Design Suite.

Figure 1-3: Xilinx Documentation Navigator

# System Design

# **Overview**

Before starting on your project, it is important to have a clear understanding of how you will design and assemble your system. In any complex system, there are multiple paths to a solution. These paths are dictated by the various choices you make on what IP blocks to create from scratch, what IP you can re-use, and the tools and methodology used to validate the IP, integrate the IP in a system, and verify the system.

This chapter addresses the system partitioning choices you will make and reviews key features of the Vivado Design Suite which help automate the process of system development.

- System Partitioning

- System Development

# **System Partitioning**

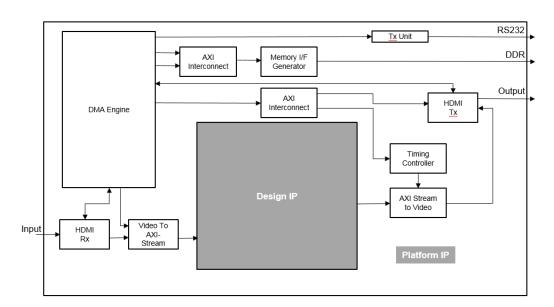

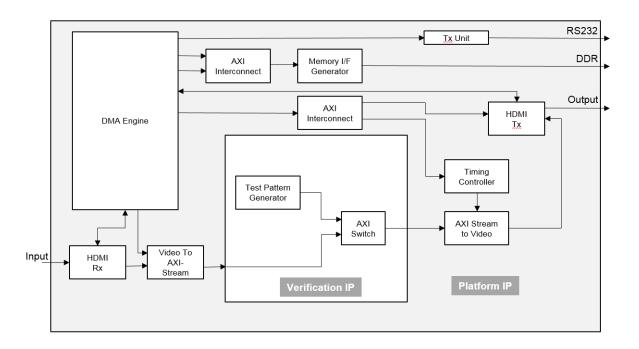

In a typical design, the logic on the periphery of the design is dedicated to interfacing with external devices, typically using standard interfaces. Example of this are DDR, Gigabit Ethernet, PCIe, HDMI, ADC/DAC, and Aurora interfaces. These interfaces and the components used to implement them are typically standard to multiple FPGA designs within the same company.

In the High-Level Productivity Design Methodology this logic is separated from the core design IP and is considered the platform. The figure below shows a platform example block design. The shaded area in the center of the figure below indicates where the design IP or platform verification IP can be added.

Figure 2-1: Platform Design Example

Key benefits of this methodology are:

- The platform is developed and verified independently of the rest of the design.

- Board-level integration and device pin planning are addressed by a separate dedicated team working in parallel.

- The platform is saved and re-used (even re-edited), allowing multiple derivative designs to be quickly realized.

- The core design IP is developed and verified independently of the platform.

- The pre-verified platform and design IP are quickly integrated into a complete system.

When partitioning your system, the first task is to determine what will be implemented in the platform and what will be implemented as core design IP.

# **Platform Design**

A platform design provides two key attributes to a high productivity methodology:

- Separating standard interface logic from the design IP, allowing the development and verification of both to proceed in parallel.

- Creating a re-usable design, or platform, that can be used to quickly create design derivatives.

A platform should ideally contain the parts of the design that are standard, such as design interfaces and interface IP. However, a platform can also contain blocks used for pre-processing or post-processing. If the processing functions are independent of the core design IP, and if the processing functions could be used across multiple designs, it is more ideal to place these blocks in the platform. The platform re-use methodology allows blocks to be easily removed from the platform.

Irrespective of the logic you decide to incorporate into the platform design, a key attribute of the platform design is that the internal interfaces, those which connect to the internal design IP, should be implemented using standard interfaces. Use of standard internal interfaces such as AXI will enhance the platform re-use by doing the following:

- Allowing the platform to be easily connected to a design IP that has yet to be developed

- Ensuring that verification of the platform also verifies the internal interfaces

- Enabling use of the high productivity integration features described in IP Integrator and Standard Interfaces, page 18

Even if you are initially only thinking of one design, a platform based methodology allows you to easily create derivative designs after the initial design is implemented.

More details about platform development and verification are described in Chapter 3, Platform Development.

# **IP Design**

The key feature of the IP development flow is that it includes only the IP that differentiates the product from the platform.

The design IP is not standard and will be developed. Much of the development effort is running simulations to validate that the design provides the correct functionality. This effort can be minimized, and simulation run times improved, by not including standard blocks that do not impact the new functionality being developed; those blocks should be in the platform.

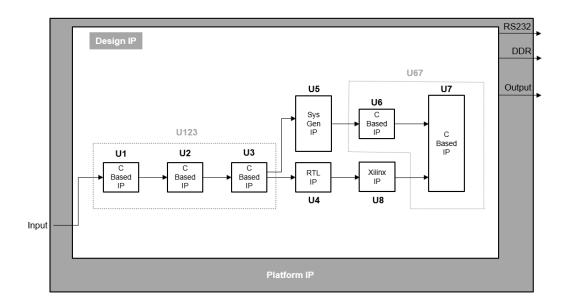

The figure below shows a representation of a complete system with design IP added to the platform design. A key feature of the completed system is that it might contain IP developed from many different sources, such as:

- IP generated from C/C++ using Vivado HLS

- IP generated from System Generator

- · IP from RTL

- Xilinx IP

- Third-Party IP

Figure 2-2: System Design Example

In a high productivity design methodology, one of the greatest benefits comes from the verification speed of C simulation. From a design creation perspective, there is large productivity gain by simulating the C blocks together during development.

- Fast C simulation allows the designer to quickly develop and verify an accurate solution.

- Multiple C blocks simulated together help each verify the output of the other.

- A larger overall productivity benefit can be achieved if several C IP are combined together in a C simulation.

The figure above, Figure 2-2, page 15, highlights a dilemma you may face when using C IP. Blocks U1, U2, and U3 are all C IP and could be grouped into a single top-level U123. Similarly, blocks U6 and U7 could be grouped into a single IP block, U67. You can do one of the following:

- Create multiple smaller C IP blocks, such as U1, U2, U3, U6 and U7.

- Create a few large C IP blocks, such as U123 and U67 outlined in the figure above.

From a design integration perspective, there is no difference between these methods; if the IP blocks are generated with AXI interfaces, they are easily integrated together using IP integrator. For designers who are new to C-based IP development, it might make more sense to work on smaller blocks, learn how to optimize each small block independently, and then integrate multiple smaller IPs together. For designers who are comfortable with C IP development, it might make more sense to generate a few large C IP blocks.

**IMPORTANT:** The key productivity benefit is being able to simulate as many C IP blocks as one C simulation during development.

In the situation described above, the same C test bench that verifies blocks U1, U2, and U3 would be used to verify U123. The difference in IP generation is that you either set the top level for C synthesis in Vivado HLS as function U123, or as function U1 followed by U2 and U3.

Regardless of which route is taken to create the IP blocks, each of the IP blocks should be verified in isolation as follows:

- IP developed from C/C++ is verified using the C/RTL co-simulation feature of Vivado HLS, allowing the RTL to be verified using the same C test bench used to verify the C test bench.

- IP developed from System Generator is verified using the MathWorks Simulink design environment provided in System Generator. The Simulink environment enables the easy generation of complex input stimuli and analysis of complex results through the use of pre-defined simulation elements. IP generated from C/C++ and through traditional RTL can be imported into the System Generator environment to take advantage of this verification.

- For IP generated from RTL, you must create an RTL test bench to verify the IP.

- IP provided by Xilinx and third-party providers is pre-verified, however you might wish to create a test bench to confirm its operation based on your own set of configuration parameters.

The use of standard AXI interfaces on the IP allows the IP to be quickly integrated, both with each other and with the platform design.

# **System Development**

Although the concept of using a platform and multiple IP blocks is not new to FGPA designers, this methodology typically requires lots of RTL to be developed and simulated, requiring stitching hundreds, if not thousands, of individual RTL signals together multiple times to make the following connections:

- · The platform to verification IP

- The platform to the core design IP

- The platform to derivative core design IP.

In lieu of the many additional man-hours in both design and verification effort it would take to use this methodology in a traditional RTL design flow (this is an error prone task when

performed in a text editor), design teams typically design and integrate everything together.

Vivado IP integrator enables this methodology and allows IPs to be quickly integrated without the traditional hand-editing of RTL files.

The key features for using this methodology are:

- Vivado IP Catalog

- IP integrator and standard interfaces

# **Vivado IP Catalog**

The Vivado IP Catalog is the backbone of any methodology that uses IP and IP re-use. Figure 2-3, page 17 shows an alternative view of the design process for the High-Level Productivity Design Methodology highlighting where and when the IP Catalog is used.

**IMPORTANT:** Use of the IP Catalog is key to enabling a High-Level Productivity Design Methodology.

Figure 2-3: IP Catalog and the Design Process

The IP Catalog has the following features:

- Includes approximately 200 IPs from Xilinx. For more information, refer to the Xilinx Intellectual Property Page [Ref 12].

- Saves the output from C based IP development.

- Can be enhanced with System Generator, legacy RTL, and Xilinx Partner IP.

- Contains a large number of interface IPs, supports the use of legacy RTL IP, and is used extensively when creating the platform.

- Is the source for all IP blocks during system integration.

- Provides the RTL implementations used during system integration and verification.

During platform development, the platform is assembled in IP integrator using IP from the IP Catalog. This might include interface IP provided by Xilinx (Ethernet, VGA, CPRI, Serial Transceivers, etc.), IP from Xilinx partners, legacy RTL package as IP for the IP Catalog, or IP created by Vivado HLS and System Generator.

Details about packaging legacy RTL as IP are provided in the *Vivado Design Suite Tutorial:* Creating and Packaging Custom IP (UG1119) [Ref 5].

Details on creating IP with AXI interfaces from System Generator are provided in the *Vivado Design Suite User Guide: Model-Based DSP Design Using System Generator* (UG897) [Ref 6].

The default output from Vivado HLS is an IP packaged for the IP Catalog. This is described in IP Packaging, page 58.

# **IP Integrator and Standard Interfaces**

The Vivado IP integrator allows IP blocks to be quickly added to a canvas and connected, and is a key enabler of a high productivity design methodology.

**IMPORTANT:** The key to high productivity using Vivado IP integrator is the use of standard interfaces.

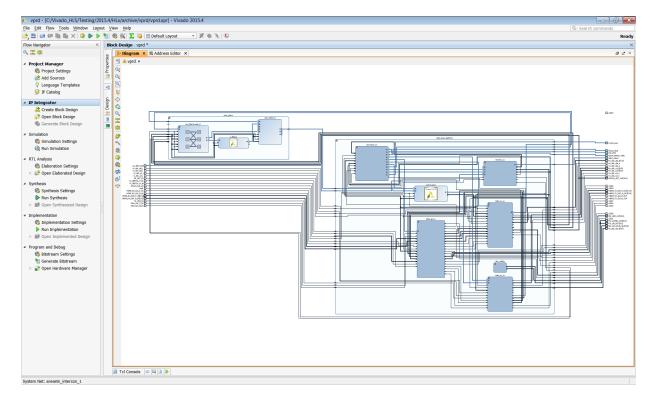

Figure 2-4, page 19 shows an example block design captured in IP integrator.

Figure 2-4: IP integrator block design

The connection types include:

- Pin-level connections such as clock and reset signals.

- Bus-level connections such as AXI, AXI-Lite and AXI-Stream buses.

- Board-level connections such as DDR.

Connections in IP integrator are made by using the mouse to graphically connect the pins on each IP together. In addition to supporting basic connecting bit-level connections, support is provided for bus-level connection and designer assistance.

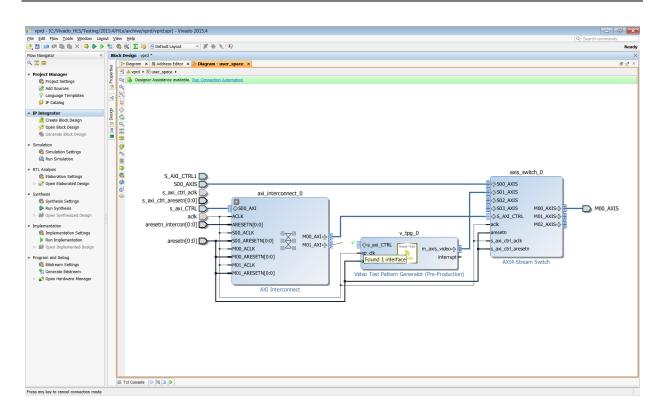

The following figure highlights the advantage of bus-level connections. In this example, two AXI master interfaces are to be connected together. Note that as soon as the connection is made to the first port, all possible valid connections are identified on the diagram by green check marks.

**IMPORTANT:** IP integrator does not allow illegal connections to be made. This eliminates the types of connectivity errors typically made when this process is performed through manual edits.

Figure 2-5: Connection Automation

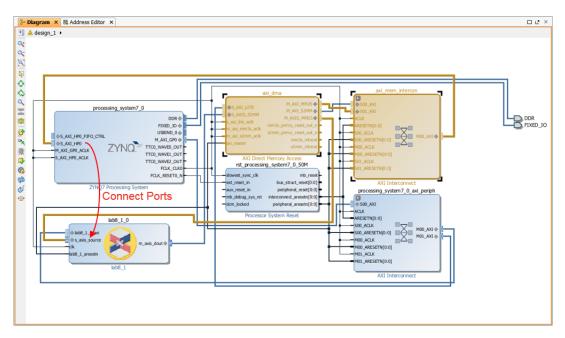

A further productivity feature provided by the use of standard AXI interfaces and IP integrator is the automatic generation of the AXI interconnect IP. Figure 2-6, page 21 shows the result when connecting:

- An AXI output on one block

- An AXI-Stream input on another block

IP integrator automatically adds the AXI Interconnect IP to connect the master type interface to a stream type interface.

Figure 2-6: Automated AXI Interconnect IP

This AXI Interconnect IP is provided in the IP Catalog and can be added manually but IP integrator automates the task. Furthermore, if the final block design is saved as a script, the Tcl commands simply state which pins to connect.

**TIP:** When you upgrade to a new release of the Vivado Design Suite and Xilinx IP, re-run the script to make sure that it uses the latest interconnect logic.

A final case for using standard interfaces in your designs is the designer assistance provided for board level connections. In addition to allowing the target device to be selected, the Vivado Design suite allows selection of target boards. IP integrator is board-aware and is able to automate board-level connections.

After confirmation from the designer, IP integrator automatically makes the connections between the IP and FPGA pins (board connections).

Figure 2-7: Block Assistance

IP integrator automates integration of IP into a block level diagram. Additional features include Design Rule Checks using the Validate feature and the automatic addition of clock and reset logic for AXI Interconnect IP. The key to taking advantage of this automation, and enabling a productive platform methodology, is the use of standard interfaces and AXI interfaces for on-chip communication.

# Platform Development

# **Overview**

The use of a platform is a critical part of the productivity benefits provided by a high productivity design methodology. A platform design contains all of the standard interfaces and processing blocks that provide the connection between the core design IP and the remainder of the system, and is developed in parallel to the core design IP.

A methodology that incorporates platform design provides key productivity gains, such as:

- It allows the development of the design interfaces and IO planning to proceed independently of the core design.

- It enables the verification of the design interfaces to start before the core design IP is ready.

- It reduces the verification time for the interfaces because the design is smaller; it does not contain the core design IP that typically represents the majority of the logic in the system.

- It promotes a highly productive design re-use methodology, allowing derivative designs to be easily created.

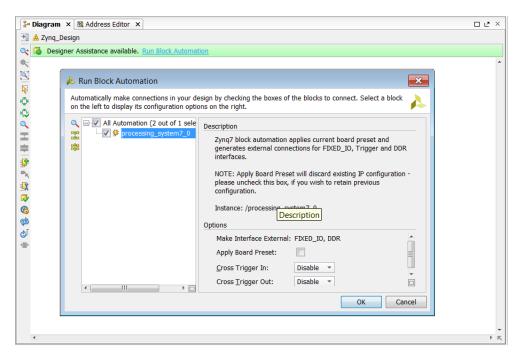

An overview of the platform design methodology is shown in Figure 3-1, page 24. A key attribute of the methodology is the re-use of the platform design.

Figure 3-1: Platform Methodology

Platform development consists of two equally important processes: platform design and platform verification.

# **Platform Design**

A platform design consists only of the design periphery, as shown in the figure above, and must be in a form that makes the design easy to re-use. The platform will be saved and re-opened to form the basis of multiple projects.

To achieve the level of design re-use required to enable the flow shown in the above figure, the platform design should be captured as a block design in IP integrator that can be easily saved and re-opened to form the basis of other design projects.

# **Assemble Existing IP**

A platform design is assembled as block design in IP integrator using IP from the IP Catalog.

**IMPORTANT:** In preparation for creating your platform, package any existing RTL or company-specific IP you want to use in the platform design as IP for use in the IP Catalog. This allows you to add the IP in the platform block design.

For details about how to package blocks for the IP Catalog, refer to the *Vivado Design Suite Tutorial: Creating and Packaging Custom IP* (UG1119) [Ref 5].

# **Platform Design Project**

After you assemble your IP, create a Vivado RTL project.

**TRAINING:** Creating a Vivado RTL project is detailed in the <u>Vivado Design Suite QuickTake Video:</u> <u>Creating Different Types of Projects.</u>

When creating the Vivado project:

- Specify the project as an RTL project and select **Do not specify any sources at this time**. The sources for the platform design are the IP you have packaged in the IP Catalog.

- Ideally, select the target as a Xilinx board. The IO for devices used on Xilinx boards has already been configured. This allows you to get started in the quickest possible time—while your own custom board is developed—and allows you to use Designer Automation within IP integrator for IO connections.

If you do not specify a Xilinx board as the target, you will also need to specify the IO connections for the target device. Refer to this link in the UltraFast Design Methodology Guide for the Vivado Design Suite (UG949) [Ref 7].

If you are using your own custom board during the development process, you might want to create a board file that details the board connections and allows designer automation within IP integrator, greatly simplifying board level connections. Details on the board file are provided in "Using the Vivado Design Suite Board Flow," provided at <a href="this link">this link</a> in the Vivado Design Suite User Guide: System-Level Design Entry (UG895) [Ref 9].

After the project has been created, use the **Create Block Design** button in the Flow Navigator to open IP integrator and create a new Block Design. In the IP integrator window, specify the source of your IP repository and use the **Add IP** button to start assembling the platform.

**TRAINING:** An overview of IP integrator is provided in the <u>Vivado Design Suite QuickTake Video:</u> Designing with Vivado IP Integrator.

Once the platform is complete, the write\_bd\_tcl command is used to save the entire Block Design as a Tcl script. This script contains everything that is needed to re-generate the block design from scratch. The Block Design and Vivado project are saved and ready for the next stages of verification and system development.

In depth information on pin planning, IP integrator, and other features in the Vivado Design Suite is provided in the Design Hubs tab of the Documentation Navigator. For more information, refer to Using the Documentation Navigator, page 10.

# **Platform Verification**

After the platform design is created, platform verification can proceed. In the verification process, the platform design is re-opened and verification IP is added to the design to confirm that the interfaces are working.

# **Platform Verification Projects**

The first step in verifying the platform design is to create a new verification project using one of the following two options.

- Open the Vivado project for the platform design and use **File > Save Project As** to save the platform design in a new project.

- Create a new Vivado RTL project (with no RTL sources) and the same target device or board. Then select **Create Block Design**, and in the console, source the Tcl script saved using write db tcl to regenerate the platform Block Design in the new project.

Multiple verification projects might be required to ensure that the complexity of the verification design is manageable. The figure below shows an example platform verification design. this example tests only a single interface.

Figure 3-2: Platform Verification Example

#### Verification IP

Verification IP is added to the platform design from the Vivado IP Catalog to verify the design.

The verification IP can be developed using any of the techniques discussed in this guide: RTL, System Generator, or C-based IP. The following examples shows how if standard AXI Interface IPs are used, a small C file can be used to quickly create, for example, a HANN window of N samples output on an AXI stream interface. An AXI memory mapped interface can be implemented by simply changing the interface directive to m\_axi from axis, as shown in the following code example:

```

void verify_IP_Hann(float outdata[WIN_LEN]) {

// Specify AXI-Stream output

#pragma HLS INTERFACE axis port=outdata

// Alternative output AXI4M (commented out)

//#pragma HLS INTERFACE m_axi port=outdata

float coeff[WIN_LEN];

coeff_loop:for (int i = 0; i < WIN_LEN; i++) {

coeff[i] = 0.5 * (1.0 - cos(2.0 * M_PI * i / WIN_LEN));

}

winfn_loop:for (unsigned i = 0; i < WIN_LEN; i++) {

outdata[i] = coeff[i];

}

}</pre>

```

For information about how to use Vivado HLS to create interface blocks between other IPs, refer to *Methods for Integrating AXI4-based IP Using Vivado IP Integrator Application Note* (XAPP1204) [Ref 10].

# Verifying the Platform

If a top-level test bench is added to the simulation sources, the platform design can be verified by simulation prior to programming the FPGA.

Verification of the platform using RTL simulation requires the creation of the RTL test bench. This same test bench is used to verify the fully integrated design. If multiple verification projects are used to verify the platform, the same test bench should be expanded to verify all of the interfaces.

To verify detailed interfaces on the FPGA, additional signal level debug probes can be added to the design.

When working in the Block Design, the right-click menu allows nets to be easily marked for debug. Signals marked for debug can be analyzed during hardware operation: ILA cores are added to the design to allow the signals to be captured and scanned out of the FPGA device for analysis. Refer to this link in the Vivado Design Suite User Guide: Designing IP Subsystems Using IP Integrator (UG994) [Ref 8].

The final design is then processed through the Vivado design flow to bitstream. When the platform is fully verified, any modifications to the platform design, other than modifications to the verification IP, should be propagated back to the original source platform design project. The platform design is then ready for the integration of the core design IP.

# C-Based IP Development

# **Overview**

In a high productivity design flow, the primary means of generating the core design IP is through the use of C-based IP and High-Level Synthesis (HLS) of C code into RTL. A C-based IP development flow provides the following benefits:

- Superior simulation speeds provided by C verification

- Automated generation of accurately timed optimized RTL

- Ability to use existing C IP from libraries

- Ease of integrating the resulting RTL IP into a complete system using IP Integrator

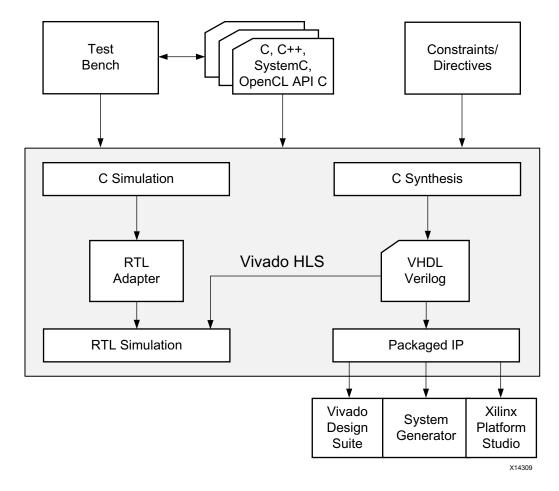

This chapter discusses how C-Based IP is created, validated, synthesized, analyzed, optimized, and packaged into IP for the IP Catalog. The means for achieving this is Vivado High-Level Synthesis (HLS), a tool provided as part of the Vivado Design Suite.

The design flow for Vivado HLS is shown in the figure below. The design flow steps are:

1. Compile, execute (simulate), and debug the C algorithm.

**Note:** In high-level synthesis, running the compiled C program is referred to as *C simulation*. Executing the C program simulates the function to validate that the algorithm is functionally correct.

- 2. Synthesize the C program into an RTL implementation, optionally using user optimization directives.

- 3. Generate comprehensive reports and analyze the design.

- 4. Verify the RTL implementation using a push button flow.

- 5. Package the RTL implementation into a selection of IP formats.

Figure 4-1: Vivado HLS Design Flow

Details about using Vivado HLS are provided in the *Vivado*® *Design Suite User Guide: High-Level Synthesis* (UG902) [Ref 2]. This chapter explains a methodology for using Vivado HLS in a highly productive manner.

# **Fast C Verification**

Simulating an algorithm in C can be orders of magnitude faster than simulating the same algorithm in RTL.

For example, consider a standard video algorithm. A typical video algorithm in C processes a complete frame of video data and compares the output image against a reference image to confirm that the results are correct. The C simulation for this typically takes 10-20 seconds. A simulation of the RTL implementation typically takes a few hours to day(s) depending on the number and complexity of the design.

The more development performed at the C level, using the simulation speed of software, the more productive you will be. It is at this level that designers actually design: adjusting their algorithm, data types, and bit-width to validate and confirm that the design is correct.

The remainder of the flow is development: using a tool chain to implement the correct design in an FPGA. The benefits provided by the Vivado Design Suite and a High-Level Productivity Design methodology is the high degree of automation provided to the development flow.

After the initial FPGA design is implemented, it is not uncommon to create an entire new bitstream to program the FPGA, using the scripted flow presented in Chapter 5, System Integration, in less time than it takes to perform a system-wide RTL simulation.

To maximize the productivity of a C-based IP flow, the following should be understood:

- The C Test Bench

- Self-Checking Test Bench

- Bit Accurate Data Types

#### The C Test Bench

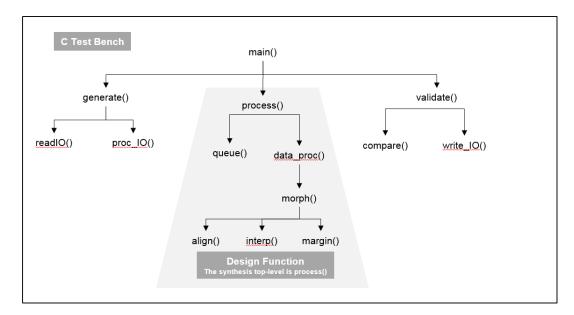

The top level of every C program is the main() function. Vivado HLS synthesizes any single function below the level of main(). The function to be synthesized by Vivado HLS is referred to as the Design Function. This is highlighted in Figure 4-2, page 32.

- All functions below the Design Function are synthesized by Vivado HLS.

- Everything outside of the Design Function hierarchy is referred to as the C test bench.

The C test bench includes all of the C code below main() that supplies input data to the Design Function and accepts output data from the Design Function to confirm that it is accurate.

Figure 4-2: C Test Bench

The single biggest mistake made by users new to a Vivado HLS design flow is to proceed to synthesize their C code without using a C test bench and performing C simulation. This can be highlighted by the following code. What is wrong with this example of nested loops?

```

#include "Nested_Loops.h"

void Nested_Loops(din_t A[N], dout_t B[N]) {

int i,j;

dint_t acc;

LOOP_I:for(i=0; i < 20; i++) {

LOOP_J: for(j=0; j < 20; j++) {

if(j=0) acc = 0;

acc += A[i] * j;

if(j=19) B[i] = acc / 20;

}

}</pre>

```

This code fails to synthesize into the expected result because the conditional statements evaluate as FALSE and J is set to 19 at the end of the first iteration of LOOP\_J. The conditional statements should be j==0 and j==19 (using == instead of ===). The preceding code example compiles, executes, and can be synthesized without any issue. However, it will not do what is expected by a cursory visual evaluation of the code.

In an era where developers consistently use one or more of C/C++, Perl, Tcl, Python, Verilog, and VHDL on a daily basis, it is hard to catch such trivial mistakes, more difficult still to catch functional mistakes, and extremely difficult and time consuming to uncover either after synthesis.

A C test bench is nothing more than a program that calls the C function to be synthesized, provides it test data, and tests the correctness of its output; this can be complied and run prior to synthesis and the expected results validated before synthesis.

You might initially feel that you are saving time by going directly to synthesis, but the benefits of using a C test bench in your design methodology are worth a lot more than the time it takes to create one.

# **Self-Checking Test Bench**

The Vivado HLS supports C simulation prior to synthesis to validate the C algorithm and C/RTL co-simulation after synthesis to verify the RTL implementation. In both cases, Vivado HLS uses the return value of function main() to confirm that the results are correct. An ideal C test bench has the result checking attributes shown in the code example below. The outputs from the function for synthesis are saved into the file results.dat and compared to the correct and expected results, which are referred to as the "golden" results in this example.

```

int main () {

int retval=0;

fp=fopen("result.dat", "w");

// Call the function for synthesis

loop perfect(A,B);

// Save the output results

for(i=0; i< N; ++i) {

fprintf(fp, "%d \n", B[i]);

} . . .

// Compare the results file with the golden results

retval = system("diff --brief -w result.dat result.golden.dat");

if (retval != 0) {

printf("Test failed !!!\n");

retval=1;

else {

printf("Test passed !\n");

// Return 0 ONLY if the results are correct

return retval;

```

In the Vivado HLS design flow, the return value to function main() indicates the following:

- A value of Zero: Results are correct.

- A Non-zero value: Results are incorrect.

**RECOMMENDED:** Because the system environment (for example, Linux, Windows, or Tcl) interprets the return value of the main() function, Xilinx recommends that you constrain the return value to an 8-bit range for portability and safety.

By using a self-checking test bench, you are not required to create an RTL test bench to verify that the output from Vivado HLS is correct. The same test bench used for the C simulation is automatically used during C/RTL co-simulation and the post-synthesis results verified by the test bench.

There are many ways in C to check that the results are valid. In the above example, the output from the function for synthesis is saved to file result.dat.and compared to a file with the expected results. The results could also be compared to an identical function not marked for synthesis (which executes in software when the test bench runs) or compared to values calculated by the test bench.

**IMPORTANT:** If there is no return statement in function main() of the test bench, the C standard dictates that the return value is zero. Thus, C and C/RTL co-simulation always reports the simulation as passing, even if the results are incorrect. Check the results and return zero only if they are correct.

The time spent to create a self-checking test bench ensures that there are no obvious errors in the C code and no requirement to create RTL test benches to verify that the output from synthesis is correct.

# Bit Accurate Data Types

Arbitrary precision data types are provided with Vivado HLS and allow variables to be specified at any width. For example, variables might be defined as 12-bit, 22-bit, or 34-bits wide. Using standard C data types, these variables are required to be 16-bit, 32-bit, and 64-bit, respectively. Using the standard C data types often results in unnecessary hardware to implement the required accuracy; for example, 64-bit hardware when only 34-bit is required.

An even greater benefit of using arbitrary precision data types is that the C algorithm can be simulated using these new bit-widths and the bit-accurate results analyzed. For example, you might wish to design a filter with 10-bit inputs and 14-bit output and you might determine that the design can use a 24-bit accumulator. Performing C simulation—which can simulate the filter with tens of thousands of samples in a matter of minutes—will quickly confirm whether the signal-to-noise ratio of the output is acceptable. You will quickly be able to determine if the accumulator is too small or verify that using a smaller, more efficient accumulator still provides the required accuracy.

**IMPORTANT:** Simulation of a bit-accurate C is the fastest way to verify your design.

A productive methodology is to start your initial design with standard C data types and confirm the algorithm performs as designed. Then migrate your C code to use arbitrary

precision data types. This migration to more hardware efficient data types can only be performed safely and productively if there is a C test bench checking the results, allowing you to quickly verify the smaller more efficient data types are adequate. Once you are comfortable with arbitrary precision types, you will typically use arbitrary precision data types right from the start of your new C project.

The benefits of using a C test bench, and the loss of productivity in not using one as part of your design methodology, cannot be overstated.

The Vivado HLS examples described at this link in the Vivado Design Suite User Guide: High-Level Synthesis (UG902) [Ref 2] are all provided with a C, C++, or SystemC test bench. These examples can be copied and modified to create a C test bench. They include C functions using arbitrary precision data types.

# C Language Support for Synthesis

Understanding what is supported for synthesis is important part of the Vivado HLS UltraFast design methodology. Vivado HLS provides comprehensive support for C, C++, and SystemC. Everything is supported for C simulation; however, it is not possible to synthesize every description into an equivalent RTL implementation.

The two key principles to keep in mind when reviewing the code for implementation in an FPGA are:

- An FPGA is a fixed size resource. The functionality must be fixed at compile time. Objects in hardware cannot be dynamically created and destroyed.

- All communication with the FPGA must be performed through the input and output ports. There is no underlying Operating System (OS) or OS resources in an FPGA.

# **Unsupported Constructs**

# System Calls

System calls are not supported for synthesis. These calls are used to interact with the OS upon which the C program executes. In an FPGA there is no underlying OS to communicate with. Example of systemcalls are time() and printf().

Some commonly used functions are automatically ignored by Vivado HLS and there is no requirement to remove them from the code. These functions are:

- abort()

- atexit()

- exit()

- fprintf()

- printf()

- perror()

- putchar()

- puts()

An alternative to removing any unsupported code is to guard it from synthesis. The \_\_SYNTHESIS\_\_ macro is automatically defined by Vivado HLS when synthesis is performed.

This macro can be used to include code when C simulation is run, but exclude the code when synthesis is performed.

```

#ifndef __SYNTHESIS__

// The following code is ignored for synthesis

FILE *fp1;

char filename[255];

sprintf(filename,Out_apb_%03d.dat,apb);

fp1=fopen(filename,w);

fprintf(fp1, %d \n, apb);

fclose(fp1);

#endif

```

**Note:** Only use the \_\_SYNTHESIS\_\_ macro in the code to be synthesized. Do *not* use this macro in the test bench, because it is not obeyed by C simulation or C RTL co-simulation.

If information is required from the OS, the data must be passed into the top-level function for synthesis as an argument. It is then the task of the remaining system to provide this information to the synthesized IP block. This can typically be done by implementing the data port as an AXI4-Lite interface connected to a CPU.

# **Dynamic Objects**

Dynamic objects cannot be synthesized. The function calls malloc(), alloc(), pre-processor free(), and C++ new and delete dynamically create or destroy memory resources that exist in the OS memory map. The only memory resources available in an FPGA are block RAMs and registers. Block RAMs are created when arrays are synthesized and the values in the arrays must be maintained over one or more clock cycles. Registers are created when the value stored by a variable must be maintained over one or more clock cycles. Arrays of a fixed size or variables must be used in place of any dynamic memory allocation.

As with restrictions on dynamic memory usage, Vivado HLS does not support (for synthesis) C++ objects that are dynamically created or destroyed. This includes dynamic polymorphism and dynamic virtual function calls. New functions, which would result in new hardware, cannot be dynamically created at run time.

For similar reasons, recursion is not supported for synthesis. All objects must be of a known size at compile time. Limited support for recursion is provided when using templates.

Except for standard data types, such as std::complex, C++ Standard Template Libraries (STLs) are *not* supported for synthesis. These libraries contain functions which make extensive use of dynamic memory allocation and recursion.

#### SystemC Constructs

An SC MODULE cannot be nested inside, or derived from, another SC MODULE.

The SC\_THREAD construct is not supported (however, SC\_CTHREAD is).

#### **Constructs with Limited Support**

#### **Top-Level Function**

Templates are supported for synthesis but are not supported for use on the top-level function.

A C++ class object cannot be to top-level for synthesis. The class must be instantiated into a top-level function.

Pointers to pointers are supported for synthesis but not when used as a argument to the top-level function.

#### **Pointer Support**

Vivado HLS supports pointer casting between native C types but does not support general pointer casting, such as casting between pointers to differing structure types.

Vivado HLS supports pointer arrays, provided that each pointer points to a scalar or an array of scalars. Arrays of pointers cannot point to additional pointers.

#### Recursion

Recursion in an FPGA is only supported through the use of templates. The key to performing recursion in synthesis is the use of a termination class, with a size of one, to implement the final call in the recursion.

#### **Memory Functions**

The memcpy() and memset() are both supported with the limitation that const values must be used.

- memcpy(): used for bus burst operation or array initialization with const values. The

memcpy function can only be used to copy values to or from arguments to the

top-level function.

- memset (): used for aggregate initialization with constant set value.

Any code which is not supported for synthesis, or for which only limited support is provided, must be modified before it can be synthesized.

More complete details on language support and are provided at <u>this link</u> in the *Vivado Design Suite User Guide: High-Level Synthesis* (UG902) [Ref 2].

# **Using Hardware Optimized C Libraries**

Vivado HLS provides a number of C libraries for commonly used C functions. The functions provided in the C libraries are generally pre-optimized to ensure high-performance and result in an efficient implementation for when synthesized.

"High-Level Synthesis C Libraries," available at this link in the Vivado Design Suite User Guide: High-Level Synthesis (UG902) [Ref 2], provides extensive details on all the C libraries provided with Vivado HLS, however it is highly recommended to have an appreciation of what C functions are available in the C libraries as part of your methodology.

Vivado HLS includes the following C libraries:

- Arbitrary Precision Data Types

- HLS Stream Library

- Math Functions

- Linear Algebra Functions

- Digital signal processing (DSP) Functions

- Video Functions

- IP Library

# **Understanding Vivado HLS**

In it crucial to understand some key HLS concepts before reviewing the subsequent sections in this guide which address optimizing C-based IP. This section provides a brief overview of those concepts.

## **Measuring Performance**

Vivado HLS quickly creates the most optimum implementation based on its own default synthesis behavior and constraints. The clock is the primary constraint and Vivado HLS uses this along with the target device specifications to determine how many operations can be performed within a clock cycle.

After satisfying the clock frequency constraint, the performance metrics used by Vivado HLS, and in order of optimization importance, are:

- **Initiation Interval (II)**: This the number of clock cycles between new inputs. This represents the throughput and how quickly the design reads the next input and processes it.

- **Latency**: This is the number of clock cycles required to generate the output. After the minimum interval has been achieved, or if no internal target has been specified, Vivado HLS seeks to minimize the latency.

- **Area**: After the minimum latency has been achieved, Vivado HLS seeks to minimize the area.

The performance metrics are reported for the entire function. For example, if the function has a scalar input, II=3 means the function is processing 1 sample every 3 clock cycles. However, if the function has an input array of N elements, II=N means N elements are processed every N clocks: a rate of one sample per clock.

Optimization directives can be used to direct Vivado HLS to create a design which prioritizes the above metrics: force a reduction in area or latency over the throughput. In the absence of any optimization directives, Vivado HLS uses these goals and the default synthesis behavior outlined below to create the initial design.

#### **Interface Synthesis**

The arguments to the top-level function are synthesized into data ports with an optional IO protocol. An IO protocol is one or more signals associated with the data port to automatically synchronize data communication between the data port and other hardware blocks in the system.

For example, in an handshake protocol, the data port is accompanied by a valid port to indicate when the data is valid for reading or writing and an acknowledge port to indicate the data has been read or written.

A full description of the IO protocols is provided at this link in the *Vivado*® *Design Suite User Guide: High-Level Synthesis* (UG902) [Ref 2], but these interfaces include AXI, AXI-Stream and AXI-Lite interfaces, allowing the IP to be easily integrated into the system using IP integrator.

In addition, an IO protocol is implemented by default for the top-level function itself. This protocol controls when the IP can start operation and indicates when the IP has completed its operation or is ready for new input data. This optional IO protocol can be implemented as an AXI-Lite interface, allowing the design to be controlled from a microprocessor.

### **Function Synthesis**

Functions are synthesized into hierarchical blocks in the final RTL design. Each function in the C code will be represented in the final RTL by a unique block. In general, optimizations stop at function boundaries; some optimization directives have a recursive option or behavior which allows the directive to take effect across function boundaries.

Functions can be inlined using an optimization directive. This permanently removes the function hierarchy and can lead to better optimization of the logic. Functions can also be pipelined to improve their throughput performance.

Functions are scheduled to execute as early as possible. The following examples shows two functions, foo 1 and foo 2.

```

void foo_1 (a,b,c,d,*x,*y) {

...

func_A(a,b,&x);

func_B(c,d,&y);

}

```

In function foo\_1, there is no data dependency between functions func\_A and func\_B. Even though they appear serially in the C code, Vivado HLS implements an architecture where both functions start to process data at the same time in the first clock cycle.

```

void foo_2 (a,b,c,*x,*y) {

int *inter1;

...

func_A(a,b,&inter1,&x);

func_B(c,d,&inter1,&y)

}

```

In function foo\_2, there is a data dependency between the functions. Internal variable inter1 is passed from func\_A to func\_B. In this case, Vivado HLS must schedule function func B to start only after function func A is finished.

#### **Loop Synthesis**

Loops by default are left "rolled." This means that Vivado HLS synthesizes the logic in the loop body once and then executes this logic serially until the loop termination limit is reached. Loops can be "unrolled" allowing all the operations to occur in parallel but creating multiple copies of the loop hardware, or they can be pipelined to improve performance.

Loops are always schedule to execute in order. In the following example, there is no dependency between loop SUM\_X and SUM\_Y, however they will always be scheduled in the order they appear in the code.

Example 4-1: Sequential Loops

#### **Logic Synthesis**

By default, the logic within functions and loops is always synthesized to execute as early as possible. Vivado HLS always seeks to minimize the latency and achieve a design. Operators in the C code, such as +, \*, and /, are synthesized into hardware cores. Vivado HLS automatically selects the most appropriate core to achieve the synthesis goals. The optimization directive RESOURCE can be used to explicitly specify which hardware core is used to implement the operation.

#### **Array Synthesis**

By default, Vivado HLS synthesizes arrays into block RAM.

In an FPGA, block RAM is provided in blocks of 18K-bit primitive elements. Each block RAM uses as many 18K primitives elements as required to implement the array. For example, an array of 1024 int types requires 1024 \* 32-bit = 32768 bits of block RAM, which requires 32768/18000 = 1.8 18K block RAM primitives to implement the block RAM. Although Vivado HLS reports that each array is synthesized into one block RAM, the block RAM might contain multiple 18K primitive block RAM elements.

By default, Vivado HLS makes no attempt to group smaller block RAMs into a single large block RAM or partition large block RAMs into smaller block RAMs. However, this is possible using optimization directives. Vivado HLS might automatically partition small arrays into individual registers to improve the quality of results.

Vivado HLS automatically determines whether to use a single or dual-port block RAM based on the synthesis goals. For example, Vivado HLS uses a dual-port block RAM if this helps to minimize the interval or latency. To explicitly specify whether to use a single or dual-port block RAM, you can use the RESOURCE optimization directive.

#### Pipelining Functions, Loops, and Tasks

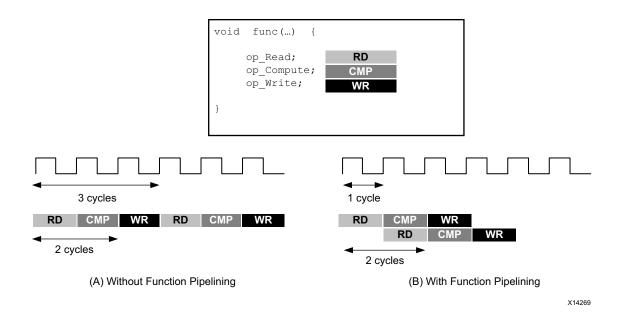

The key to achieving a high performance design is to use the PIPELINE and DATAFLOW optimization directives to pipeline functions, loops and tasks.

The following figure shows a conceptual explanation of pipelining. Without pipelining, the operations execute sequentially until the function completes. Then the next execution of the function, or the next transaction, is performed. With pipelining, the next second transaction starts as soon as the hardware resource becomes available.

Figure 4-3: Pipelining Behavior

The PIPELINE directive can be used on functions or loops to improve the throughput (minimize the II) with minimal area overhead.

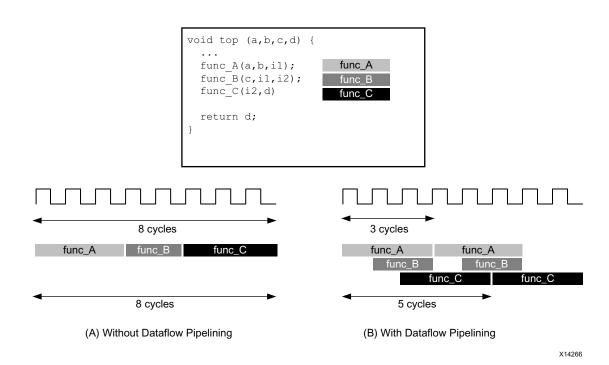

Functions and loops are considered tasks. The DATAFLOW directive can be used to "pipeline" tasks, allowing them to execute concurrently if data dependencies allow.

Figure 4-4, page 44 shows a conceptual view of task pipelining. After synthesis, the default behavior is to execute and complete func\_A, then func\_B, and finally func\_C. However, you can use the DATAFLOW optimization directive to schedule each function to execute as soon as data is available.

In this example, the original function has a latency and interval of 8 clock cycles. When you use dataflow optimization, the interval is reduced to only 3 clock cycles. The tasks shown in this example are functions, but you can perform dataflow optimization between functions, between functions and loops, and between loops.

Figure 4-4: Dataflow Optimization

#### Vivado HLS Resources

The Vivado HLS Design Hub in the Documentation Navigator provides easy access to learn more about Vivado HLS:

- QuickTake videos explaining the operation

- Tutorials on every aspect of the design flow

- The Vivado HLS User Guide

- Multiple Application Notes

For more information about design hubs, refer to Using the Documentation Navigator, page 10.

# **Optimization Methodology**

In addition to the default synthesis behavior discussed in the previous section, Vivado HLS provides a number of optimization directives and configurations that are used to direct synthesis towards a desired outcome. This section outlines a general methodology for optimizing your design for high-performance.

There are many possible goals when trying to optimize a design using Vivado HLS. The methodology assumes you want to create a design with the highest possible performance, processing one sample of new input data every clock cycle, and so addresses those optimizations before those used for reducing latency or resource.

The next section, The HLS Optimization Methodology, addresses how to apply the methodology described here for different C code architectures.

Detailed explanations of the optimizations discussed here are provided in the following sections of the *Vivado® Design Suite User Guide: High-Level Synthesis* (UG902) [Ref 2]:

- "Managing Interfaces," available at this link.

- "Design Optimization," available at this link.

It is highly recommended to review the methodology and obtain a global perspective of high-level synthesis optimization before reviewing the details of specific optimization.

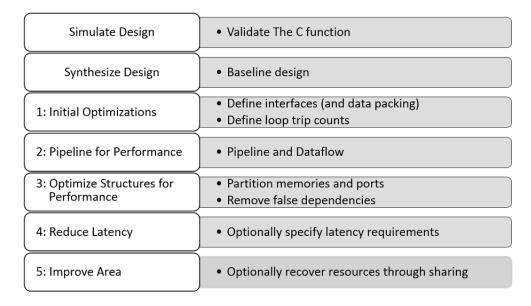

## The HLS Optimization Methodology

The optimization methodology for Vivado HLS is shown in Figure 4-5, page 46. It cannot be overstated how important it is to first verify your C code is functionally correct. The remaining steps are explained below and can be summarized as: determine your interfaces, pipeline the design, address issues which prevent optimal pipelining by optimizing data structures and then address any latency and area concerns.

Figure 4-5: HLS Optimization Methodology

The following is a complete list of optimization directives. This list shows the Tcl commands on the left side and the equivalent pragma directives, which can be placed directly in the C code, on the right:

```

set_directive_allocation - Directive ALLOCATION

set_directive_array_map - Directive ARRAY_MAP

set_directive_array_partition - Directive ARRAY_PARTITION

set_directive_array_reshape - Directive ARRAY_PARTITION

set_directive_data_pack - Directive DATA_PACK

set_directive_dataflow - Directive DATAFLOW

set_directive_dependence - Directive DEPENDENCE

set_directive_dependence - Directive EXPRESSION_BALANCE

set_directive_function_instantiate - Directive FUNCTION_INSTANTIATE

set_directive_inline - Directive INLINE

set_directive_interface - Directive INTERFACE

set_directive_latency - Directive LATENCY

set_directive_loop_flatten - Directive LOOP_FLATTEN

set_directive_loop_merge - Directive LOOP_TRIPCOUNT

set_directive_occurrence - Directive PIPELINE

set_directive_pipeline - Directive PROTOCOL

set_directive_reset - Directive RESET

set_directive_top - Directive TOP

set_directive_unroll - Directive UNROLL

```

Configurations modify the default synthesis behavior. There are no pragma equivalents for the configurations. In the GUI, configurations are set using the menu **Solution** > **Solution Settings** > **General.** A complete list of the available configurations is:

```

config_array_partition

config_bind

config the options for binding

config_compile

config the optimization

config_dataflow

config the dataflow pipeline

config_interface

config command for io mode

config_rtl

config the options for RTL generation

config_schedule

config scheduler options

```

Having a list of all the optimization directives and synthesis configurations is good. Having a methodology to use them is better.

#### **Step 1: Initial Optimizations**

The following table shows the first directives you should think about adding to your design.

Table 4-1: Optimization Strategy Step 1: Initial Optimizations

| Directives and Configurations | Description                                                                                                                                            |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERFACE                     | Specifies how RTL ports are created from the function description.                                                                                     |

| DATA_PACK                     | Packs the data fields of a struct into a single scalar with a wider word width.                                                                        |

| LOOP_TRIPCOUNT                | Used for loops which have variables bounds. Provides an estimate for the loop iteration count. This has no impact on synthesis, only on reporting.     |

| Config Interface              | This configuration controls IO ports not associated with the top-level function arguments and allows unused ports to be eliminated from the final RTL. |

The design interface is typically defined by the other blocks in the system. Since the type of IO protocol helps determine what can be achieved by synthesis it is recommended to use the INTERFACE directive to specify this before proceeding to optimize the design.

If the algorithm accesses data in a streaming manner, you might want to consider using one of the streaming protocols to ensure high performance operation.

**TIP:** If the I/O protocol is completely fixed by the external blocks and will never change, consider inserting the INTERFACE directives directly into the C code as pragmas.

When structs are used in the top-level argument list they are decomposed into separate elements and each element of the struct is implemented as a separate port. In some case it is useful to use the DATA\_PACK optimization to implement the entire struct as a single data word, resulting in a single RTL port. Care should be taken if the struct contains large arrays. Each element of the array is implemented in the data word and this might result in a very wide data ports.

A common issue when designs are first synthesized is report files showing the latency and interval as a question mark "?" rather than as numerical values. If the design has loops with variable loop bounds Vivado HLS cannot determine the latency.

Use the analysis perspective or the synthesis report to locate the lowest level loop for which synthesis fails to report a numerical value and use the LOOP\_TRIPCOUNT directive to apply an estimated tripcount. This allows values for latency and interval to be reported and allows solutions with different optimizations to be compared.

**Note:** Loops with variable bounds cannot be unrolled completely and prevents function and loops above them in the hierarchy from being pipelined. This is discussed in the next section.

Finally, global variables are generally written to and read from, within the scope of the function for synthesis and are not required to be IO ports in the final RTL design. If a global variable is used to bring information into or out of the C function you might wish to expose them as an IO port using the interface configuration.

#### **Step 2: Pipeline for Performance**

The next stage in creating a high performance design is to pipeline the functions, loops, and tasks. The following table shows the directives you can use for pipelining.

Table 4-2: Optimization Strategy Step 2: Pipeline for Performance

| Directives and Configurations | Description                                                                                                                |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| PIPELINE                      | Reduces the initiation interval by allowing the concurrent execution of operations within a loop or function.              |

| DATAFLOW                      | Enables task level pipelining, allowing functions and loops to execute concurrently. Used to minimize interval.            |

| RESOURCE                      | Specifies a resource (core) to use to implement a variable (array, arithmetic operation, or function argument) in the RTL. |

| Config Compile                | Allows loops to be automatically pipelined based on their iteration count.                                                 |

At this stage of the optimization process you want to create as much concurrent operation as possible. You can apply the PIPELINE directive to functions and loops. You can use the DATAFLOW directive at the level that contains the functions and loops to make them work in parallel.

A recommended strategy is to work from the bottom up and be aware of the following:

- Some functions and loops contain sub-functions. If the sub-function is not pipelined, the function above it might show limited improvement when it is pipelined. The non-pipelined sub-function will be the limiting factor.

- Some functions and loops contain sub-loops. When you use the PIPELINE directive, the directive automatically unrolls all loops in the hierarchy below. This can create a great deal of logic. It might make more sense to pipeline the loops in the hierarchy below.

- Loops with variable bounds cannot be unrolled, and any loops and functions in the hierarchy above these loops cannot be pipelined. To address this issue, pipeline these loops, and use DATAFLOW optimization to maximize the performance of the function that contains the loop. Alternatively, rewrite the loop to remove the variable bound.

The basic strategy at this point in the optimization process is to pipeline the tasks (functions and loops) and as much as possible. For detailed information on which functions and loops to pipeline and where to apply the DATAFLOW directive, refer to Optimization Strategies, page 55.

For designs with many loops or many nested loops, the compile configuration provides a way to automatically pipeline all the loops in the design based on their loop iteration count. For more information, refer to this link in the Vivado® Design Suite User Guide: High-Level Synthesis (UG902) [Ref 2].

Although not commonly used, you can also apply pipelining at the operator level. For example, wire routing in the FPGA can introduce large and unanticipated delays that make it difficult for the design to be implemented at the required clock frequency. In this case, you can use the RESOURCE directive to pipeline specific operations, such as multipliers, adders and block-RAM.

The RESOURCE directive specifies which hardware cores to use to implement the operations in the C code. Specifying that a resource is implemented with a latency greater than 1 causes Vivado HLS to use additional pipeline stages for the operation. RTL synthesis can use these additional pipeline stages to improve the overall timing.

The following operations support pipelined implementations:

- Standard arithmetic operations for which there is a multi-stage (\*nS) core available

- Floating-point operations

- Arrays implemented with a block RAM

### **Step 3: Optimize Structures for Performance**

C code can contain descriptions that prevent a function or loop from being pipelined with the required performance. In some cases, this might require the a code modification but in most cases these issues can be address using other optimization directives.

The following example shows a case where an optimization directive is used to improve the performance of pipelining. In this initial example, the PIPELINE directive is added to a loop to improve the performance of the loop.

```

#include "bottleneck.h"

dout_t bottleneck(din_t mem[N]) {

dout_t sum=0;

int i;

SUM_LOOP: for(i=3;i<N;i=i+4)

#pragma HLS PIPELINE

sum += mem[i] + mem[i-1] + mem[i-2] + mem[i-3];

return sum;

}</pre>

```

When the code above is synthesized the following message is output:

```

@I [SCHED-61] Pipelining loop 'SUM_LOOP'.

@W [SCHED-69] Unable to schedule 'load' operation ('mem_load_2', bottleneck.c:57) on array 'mem' due to limited memory ports.

@I [SCHED-61] Pipelining result: Target II: 1, Final II: 2, Depth: 3.

```

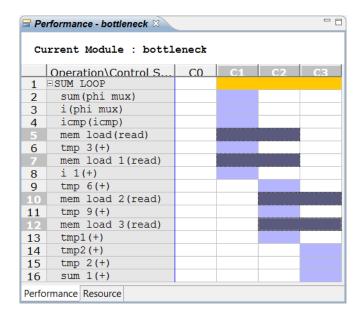

When pipelining fails to meet the required performance, the key to addressing the issue is to examine the design in the analysis perspective. Details on using the Analysis Perspective are provided at <a href="mailto:this link">this link</a> in the Vivado® Design Suite User Guide: High-Level Synthesis (UG902) [Ref 2]. The view of this design example in the analysis perspective is shown in the figure below.

- The memory (block-RAM) accesses are highlighted in the figure. These correspond the array mem in the code above.

- Each access takes two cycles: one to generate the address and one to read the data.

- Only two memory reads can start in cycle C1 because a block RAM only has a maximum of two data ports.

- The third and forth memory reads can only start in cycle C2.

- The earliest the next set of memory reads can occur is starting in cycle C3. This mean the loop can only have an II=2: the next set of inputs to the loop can only be read every two cycles.

Figure 4-6: Pipelining Fails Due to Too Few Ports

This issue can be solved by using the ARRAY\_PARTITION directive. This directive partitions arrays into smaller arrays providing more data ports and improve the data structures to allow a higher performance pipeline.

With the additional directive shown below, array mem is partitioned in 2 memories and all four reads can occur in one clock cycle. There are multiple options to partition an array. In this case cyclic partitioning with a factor of 2 ensure the first partition contain elements 0,2,4 etc. from the original array and the second partition to contain elements 1,3,5, etc.). With a dual-port block-RAM this allows elements 0,1,2 and 3 to be read in a single clock cycle.

```

#include "bottleneck.h"

dout_t bottleneck(din_t mem[N]) {

#pragma HLS ARRAY_PARTITION variable=mem cyclic factor=2 dim=1

dout_t sum=0;

int i;

SUM_LOOP: for(i=3;i<N;i=i+4)

#pragma HLS PIPELINE

sum += mem[i] + mem[i-1] + mem[i-2] + mem[i-3];

return sum;

}</pre>

```