# Application Note AN-59 LYTSwitch<sup>-</sup>4 Family

Design Guide

# Introduction

The LYTSwitch-4 family of devices are highly integrated monolithic switching ICs optimized to provide an isolated, dimmable (NEMA complaint), high power factor (PF), constant current driver for LED lighting applications at output powers of up to 78 W applications. LYTSwitch-4 devices reduce circuit complexity by integrating the power MOSFET and controller plus eliminating the optocoupler and all secondary side feedback components.

The LYTSwitch-4 devices are divided into two families as shown in Table 1, that is LYT4x1x for low-line and LYT4x2x for high-line applications each having a selection of dimmable (LYT43xx) and non-dimmable (LYT42xx) parts.

| Part Number     | Input Voltage Range | TRIAC Dimmable |

|-----------------|---------------------|----------------|

| LYT4211-LYT4218 | 85-132 VAC          | No             |

| LYT4311-LYT4318 | 85-132 VAC          | Yes            |

| LYT4221-LYT4228 | 160-300 VAC         | No             |

| LYT4321-LYT4328 | 160-300 VAC         | Yes            |

Table 1. Device Part Number Selection.

Each member of the family has a high-voltage power MOSFET and its controller integrated onto the same die. The continuous conduction mode (CCM), variable duty cycle, constant frequency operation provides both high power factor (>0.9), compliance to IEC 6100-3-2 Class C and D harmonic current limits, high efficiency and reduced EMI filtering requirements. Primary-side switching current is internally sensed eliminating external current sense resistors. Internal start-up bias current is drawn from a high-voltage current source connected to the DRAIN pin, eliminating the need for external start-up components. The internal oscillator is frequency modulated (jitter) to reduce EMI. In addition, the ICs have integrated functions that provide system-level protection. The auto-restart function limits dissipation in the device, the transformer and the output diode during overload, output short-circuit and open-loop conditions, while the auto-recovering hysteretic thermal shutdown function disables MOSFET switching during a thermal fault.

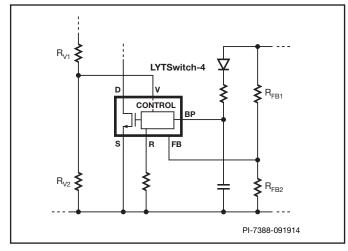

# **Basic Circuit Configuration**

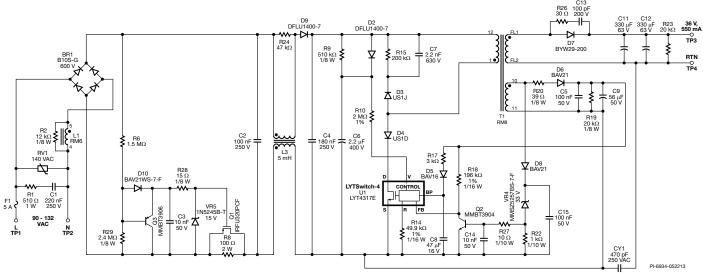

The circuit in Figure 1 shows the basic configuration of a standard AC TRIAC dimmable LED driver using LYT4317E. The circuit uses the flyback topology and with the high level integration of LYTSwitch-4 device, far fewer design issues are left to be addressed externally, resulting in one common circuit configuration for all output specifications. For example, different output power levels may require different values for some circuit components, but the circuit configuration stays unchanged.

# Scope

This application note is intended for engineers designing an isolated AC-DC LED driver using the LYTSwitch-4 family of devices. It provides guidelines to enable an engineer to quickly select key components and also complete a suitable transformer design. To simplify the task, this application note refers directly to the PIXIs design spreadsheet that is part of the PI Expert<sup>™</sup> design software suite.

Figure 1. Typical Circuit Example (DER-350) for a 25 W Dimmable LED Driver using a LYTSwitch-4 Device.

In addition to this application note the reader may also find the product Reference Design Kits (RDKs) useful. These contain a prototype board, a link to an engineering report that contains complete design information and test data and product samples. Further details on downloading PI Expert, RDKs and updates to this document can be found at Power Integrations' website www.powerint.com.

# **Quick Start**

Readers who want to start immediately can use the following information to quickly design the transformer and select the components for a first prototype. Only the information described below needs to be entered into the PIXIs spreadsheet, other parameters will be automatically selected based on a typical design. References to spreadsheet cell locations are provided in square brackets [cell reference].

- Select either TRIAC dimming (YES) or non-dimming/PMW dimming (NO) configuration [B3]. For LYTSwitch-4 (LYT-4X1X) Low Line Family selecting TRIAC dimming the value of the R pin resistor (R14 in Figure 1) is 49.9 k $\Omega$ , 1% and for non-dimming 24.9 k $\Omega$ , 1%. While for the LYTSwitch-4 (LYT-4X2X) High Line Family the value of the R pin resistor is 24.9 k $\Omega$ , 1% be it for TRIAC dimming or non-dimming configuration.

- Enter AC input voltage range VAC<sub>MIN</sub>, VAC<sub>MAX</sub> and minimum line frequency fL [B4, B5, B6] based on Table 1.

- Enter nominal output (LED string) voltage V<sub>o</sub> [B7], maximum output voltage V<sub>o(MAX)</sub> [B8] and minimum output voltage V<sub>o(MIN)</sub> [B9]. Ratio of V<sub>o(MAX)</sub>/V<sub>o(MIN)</sub> should be less than  $\leq$  1.66 (V<sub>o</sub> ±25%).

- Enter the nominal output (LED string) current IO [B11].

- Enter efficiency estimate η [B13] based on Table 3.

- Select LYTSwitch-4 device from the drop down list or enter directly [B18]. Use Table 4 for guidance based on input voltage and output power. Where a choice between two devices exists it is recommended to select the larger device and operate in reduced current limit mode for higher efficiency.

- Select the device Current Limit Mode operating mode that will be used. Enter [B20] either reduced (RED) or full (FULL). Reduced is recommended for maximum efficiency (smallest enclosure size and heat sinking) e.g. A19 retro-fit lamp applications.

- Enter V<sub>D</sub> [B32], the forward voltage of the expected output diode. Use 0.5 V for Schottky barrier types and 0.8 V for PN types.

- Enter the desired core type from the drop down menu or directly [B46]. Entering Auto will select a core size suitable for the specified output power. If the desired core is not listed, then you may enter a core's characteristics A<sub>E</sub>, L<sub>E</sub> and A<sub>L</sub> ([B48], [B49], [B50]). Enter in the bobbin width BW [B51].

- If margin tape is required (non-triple insulated wire, isolated output design), then enter the margin tape width in [B52]. Note: This will reduce the winding width by two times the margin tape width entered. For 230 VAC applications a value of 3.2 mm is typical and for 100 VAC / 115 VAC use 2 mm. In practice triple insulated wire is used in most isolated designs to minimize the size of the transformer due to limited space.

- Verify that the core's gap L<sub>g</sub> [D79], the wire gauge AWG [D84] and the primary's winding current density CMA [D86] are

within acceptable limits. Follow the guidance provided in column F to achieve this.

- Once all warning and errors have been addressed click on the Transformer Parameter and Transformer Construction tabs to obtain detailed transformer specification and construction details. These can be used to either construct the transformer in house or send to an external magnetic vendor.

- Using PIV<sub>s</sub> [D102] and I<sub>o</sub> [B11] determine the proper output rectifier. Select a diode with a voltage (V<sub>RRM</sub>) rating >PIV<sub>s</sub> and current rating >I<sub>o</sub> with a recommendation of  $\ge 2 \times I_o$  for higher efficiency.

- The value of I<sub>RIPPLE</sub> [D93] and V<sub>O(MAX)</sub> [D8] should be used to select the appropriate output capacitor. The selected capacitor should have a ripple current rating >I<sub>RIPPLE</sub> and voltage rating >V<sub>O(MAX)</sub>.

The value of the VOLTAGE MONITOR pin resistor (R<sub>v</sub>) and if

- The value of the VOLTAGE MONITOR pin resistor (R<sub>v</sub>) and if used the second lower VOLTAGE MONITOR pin resistor (R<sub>v</sub>) are provided in cells [D27] and [D28]. A value for R<sub>v2</sub> >10 M $\Omega$  indicates that it is not required.

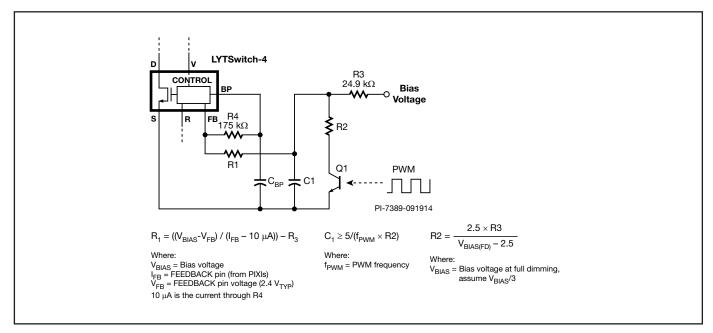

- The value of the REFERENCE pin resistor (R14 in Figure 1) programs TRIAC dimming or non-dimming. The value for the feedback resistor (R<sub>FB1</sub>) is given in cell [D30]. This is the resistor connected from the FEEDBACK pin to the bias supply and is used to sense the output voltage.

- Using  ${\rm I}_{\rm AVG}$  [E64] determine the required input filter inductor current rating.

- If necessary, the output current can be fine-tuned. After the first prototype is built and running, enter the output current in cells [B112] and [B113] at line voltages [B110] and [B111], new values for R<sub>v1</sub> and R<sub>v2</sub> are then calculated [B114], [B115]. With these values adjusted measure and enter values for the bias voltage V<sub>B1</sub> and V<sub>B2</sub> [B122], [B123] and associated output current I<sub>o1</sub> and I<sub>o2</sub> [D124], [D125]. An adjusted value for R<sub>FB1(NEW)</sub> and R<sub>FB2(NEW)</sub> [D126], [D127] (if needed) will be calculated.

# Step-by-Step Design Procedure

$\begin{array}{l} \textbf{Step 1. Enter Application Variables (Figure 4): Dimming,} \\ \textbf{VAC}_{\text{MIN}}, \textbf{VAC}_{\text{MAX}}, \textbf{f}_{\text{L}}, \textbf{V}_{\text{O}}, \textbf{V}_{\text{O(MAX)}}, \textbf{VO}_{(\text{MIN})}, \textbf{V}_{\text{OVP}}, \textbf{I}_{\text{O}}, \eta, \textbf{V}_{\text{B}} \end{array} \right.$

# Dimming Required [B3]: YES, NO

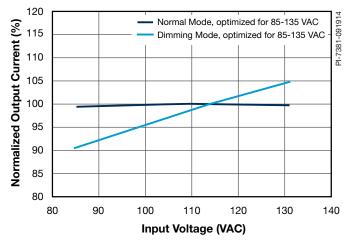

Enter YES, if the driver is to be used with TRIAC phase angle based AC dimmers else enter NO (including for PWM dimming). This input determines the configuration of the VOLTAGE MONITOR pin and REFERENCE pin resistors. The value of the REFERENCE pin resistor configures the part into either (TRIAC) dimming mode or normal mode. Dimming mode reduces the amount of input line voltage compensation to improve the dimming range obtained with TRIAC based phase angle dimmers. In this mode the output current regulation is maintained within narrow limits only over a single input voltage range (e.g. 85 VAC - 132 VAC or 185 VAC – 265 VAC). Below this input range the output current will reduce (equivalent to reduced conduction angle of a TRIAC dimmer) and above this range the output current will increase.

The normal (non-dimming) mode provides input line voltage compensation that maintains output current regulation within narrow limits across input voltage ranges (e.g. 85 VAC - 132 VAC or 185 VAC - 265 VAC). This mode does not prevent the device

Figure 2. Comparison of Output Current Regulation in Dimming and Normal Modes Versus Line Voltage. Typical Single Input Voltage Operating Ranges Shown Above (85-132 VAC).

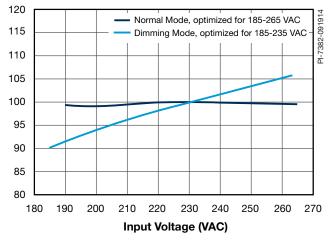

from being used with AC phase dimmers however dimming range is reduced. Figures 2 and 3 show a summary of the expected output current regulation performance versus line voltage between the two operating modes.

# Input Voltage and Line Frequency, $VAC_{MIN}$ [B4], $VAC_{MAX}$ [B4], $f_{L}$

Select the input voltage and line frequency from Table 2. For TRIAC dimming designs a single input voltage specification is preferred as this allows greater design optimization. For example a single input 100 VAC / 115 VAC versus a universal input design requires lower voltage components, smaller safety spacing requirements and reduced TRIAC bleeder current. This allows the design to offer smaller size, lower cost, broader TRIAC dimming specifications there is no efficiency. For non-TRIAC dimming specifications there is no efficiency benefit for a single input line voltage specification. This is due to the elimination of the damper and bleeder networks in non-dimming designs.

Figure 3. Comparison of Output Current Regulation in Dimming and Normal Modes Versus Line Voltage. Typical Single Input Voltage Operating Ranges Shown Above (185-265 VAC).

However the component rating, size and safety spacing benefits still apply for a single low-line vs. a universal input specification.

### Nominal Output Voltage [B7], V<sub>o</sub> (V)

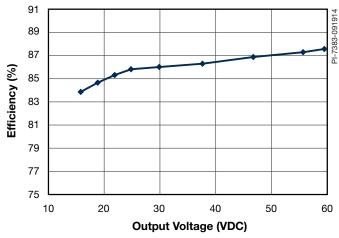

Enter the nominal output voltage of the LED string to be driven. LYTSwitch-4 based drivers are optimized to cover an output voltage range of 2:1. Higher output voltages result in higher overall efficiency due to a reduction in secondary diode and winding losses. Figure 5 shows an example of this effect for a non-TRIAC dimmable 14 W output, 100 VAC / 115 VAC input design using an RM8 core size for the transformer.

For a TRIAC dimmable design the values would reduce by ~3% due to the losses in the TRIAC compatibility damper and bleeder circuit blocks.

# Maximum Output Voltage [B8], V<sub>O(MAX)</sub> (V)

Enter the maximum LED string voltage to be driven including tolerance. If left blank a value of  $1.1 \times V_0$  is assumed.

| ENTER APPLICATION VARIABLES |       |       |    | Design Title                                                       |

|-----------------------------|-------|-------|----|--------------------------------------------------------------------|

| Dimming required            | YES   | YES   |    | Select 'YES' option if dimming is required. Otherwise select 'NO'. |

| VACMIN                      | 85    | 85    | V  | Minimum AC Input Voltage                                           |

| VACMAX                      | 132   | 132   | V  | Maximum AC input voltage                                           |

| fL                          |       | 60    | Hz | AC Mains Frequency                                                 |

| VO                          | 36.00 | 36.00 | V  | Typical output voltage of LED string at full load                  |

| VO_MAX                      |       | 39.60 | V  | Maximum expected LED string Voltage.                               |

| VO_MIN                      |       | 32.40 | V  | Minimum expected LED string Voltage.                               |

| V_OVP                       |       | 43.56 | V  | Overvoltage protection setpoint                                    |

| Ю                           | 0.700 | 0.700 | A  | Typical full load LED current                                      |

| PO                          |       | 25.2  | W  | Output Power                                                       |

| n                           | 0.88  | 0.88  |    | Estimated efficiency of operation                                  |

| VB                          |       | 25.00 | V  | Bias Voltage                                                       |

Figure 4. Application Variables Section of the Design Spreadsheet.

| Nominal Input<br>Voltage (VAC) | Minimum Line<br>Voltage (VAC <sub>MIN</sub> ) | Maximum Line<br>Voltage (VAC <sub>MAX</sub> ) | Nominal Line<br>Frequency (f <sub>L(NOM)</sub> (Hz) | Notes                                                                     |

|--------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|

| 100/115                        | 85                                            | 132                                           | 50                                                  | VAC <sub>MIN</sub> , f <sub>L(NOM)</sub> : Japan VAC <sub>MAX</sub> : USA |

| 230/240                        | 195                                           | 264                                           | 50                                                  | Europe/rest of world                                                      |

| 208/277                        | 177                                           | 320                                           | 60                                                  | Lighting in commercial buildings in USA, (208 VAC phase to phase)         |

Table 2. Standard Worldwide Input Line Voltages and Line Frequencies.

| Nominal             | Efficiency Estimate (%)  |                      |                      |                      |  |  |  |  |

|---------------------|--------------------------|----------------------|----------------------|----------------------|--|--|--|--|

| <b>Output Power</b> | TRIAC I                  | Dimming              | Non-TRIAC Dimming    |                      |  |  |  |  |

| (W)                 | (W) V <sub>o</sub> ≤12 V | V <sub>o</sub> >12 V | V <sub>o</sub> ≤12 V | V <sub>o</sub> >12 V |  |  |  |  |

| ≤3                  | 45                       | 55                   | 55                   | 65                   |  |  |  |  |

| 3-6                 | 65                       | 77                   | 78                   | 82                   |  |  |  |  |

| 6-10                | 76                       | 78                   | 80                   | 83                   |  |  |  |  |

| 10-20               | 82                       | 85                   | 85                   | 88                   |  |  |  |  |

| >20                 | 83                       | 86                   | 86                   | 89                   |  |  |  |  |

Table 3. Initial Efficiency Estimates for a New Design.

| Output Power Ta | able                                 |                                      |          |                                      |                          |

|-----------------|--------------------------------------|--------------------------------------|----------|--------------------------------------|--------------------------|

| Product         | Minimum Output<br>Power <sup>3</sup> | Maximum Output<br>Power <sup>4</sup> | Product  | Minimum Output<br>Power <sup>3</sup> | Maximum Output<br>Power⁴ |

| LYT4x11E        | 2.5 W                                | 12 W                                 | LYT4x21E | 6 W                                  | 12 W                     |

| LYT4x12E        | 2.5 W                                | 15 W                                 | LYT4x22E | 6 W                                  | 15 W                     |

| LYT4x13E        | 3.8 W                                | 18 W                                 | LYT4x23E | 8 W                                  | 18 W                     |

| LYT4x14E        | 4.5 W                                | 22 W                                 | LYT4x24E | 9 W                                  | 22 W                     |

| LYT4x15E        | 5.5 W                                | 25 W                                 | LYT4x25E | 11 W                                 | 25 W                     |

| LYT4x16E        | 6.8 W                                | 35 W                                 | LYT4x26E | 14 W                                 | 35 W                     |

| LYT4x17E        | 8.0 W                                | 50 W                                 | LYT4x27E | 19 W                                 | 50 W                     |

| LYT4x18E        | 18 W                                 | 78 W                                 | LYT4x28E | 33 W                                 | 78 W                     |

Figure 4. Device Family Power Table for Initial Device Selection.

# Minimum Output Voltage [B9], $V_{O(MIN)}$ (V)

Enter the minimum LED string voltage. If left blank a value of  $0.9 \times V_{o}$  is assumed.

# Nominal Output Current [B11], I<sub>o</sub> (A)

Enter the nominal output current the LED string is to be driven with.

# Nominal Output Power [D12], Po (W)

The calculated nominal output power.

#### Power Supply Efficiency [B13], $\eta$

Enter the estimated efficiency of the complete power supply measured at the output terminals under full load conditions and worst-case line (generally lowest input voltage). Initial values are provided in Table 3. Measure the efficiency of the first prototype board at nominal output power and both VAC<sub>MIN</sub> and VAC<sub>MAX</sub> if the measured efficiency is lower than estimated then enter the measured value and refine the transformer design.

#### Bias Voltage, $V_{B}(V)$

This entry determines the output voltage from the bias winding. For non TRIAC dimming designs a value of 20 V is recommended and 25 V where TRIAC dimming is required. The higher voltage ensures adequate voltage to supply the IC at the minimum LED string voltage and with a TRIAC dimmer at minimum conduction angle (<30 degrees).

Figure 5. Effect of Output Voltage on Efficiency, Measured on 9 Isolated Flyback Designs (15W, RM7 Core Size, Non-dimming Design Measured at 230 VAC).

The current limit mode selection defines the value of the BYPASS pin capacitor: 47  $\mu F$  for reduced and 4.7  $\mu F$  for full current limit mode.

The recommended maximum operating device temperature under worst-case conditions (input line and external product ambient temperature) is 100 °C for the tightest output current distribution over production, and 115 °C to provide adequate design margin and ensure thermal shutdown is not triggered.

**Upper V Pin Resistor Value [B27],**  $R_v$ ,  $M\Omega$  (Entry Optional) If left blank a default value of 2 M $\Omega$  is used for both dimming and non-dimming designs. In conjunction with the lower VOLTAGE MONITOR pin resistor ( $R_{v2}$ ) these values provide the best output current regulation for non-dimming and without  $R_{v2}$ , the widest dimming range in dimmable applications.

In Figure 1  $R_v$  is R10, a 1% or better tolerance should be used to obtain the narrowest output current tolerance. The voltage

| ENTER LYTSwitch-4 VARIABLES |          |               |        |                                                                                       |

|-----------------------------|----------|---------------|--------|---------------------------------------------------------------------------------------|

| LVTSwitch 4                 | LYT4X17  | 1 1 1 1 2 1 7 |        | Selected LYTSwitch-4. Part number will change based on dimming/non-dimming            |

| LYTSwitch-4                 | LY 14X17 | LYT4317       |        | application.                                                                          |

| Current Limit Mode          | RED      | RED           |        | Select "RED" for reduced Current Limit mode or "FULL" for Full current limit mode     |

| ILIMITMIN                   |          | 2.35          | A      | Minimum current limit                                                                 |

| ILIMITMAX                   |          | 2.73          | A      | Maximum current limit                                                                 |

| fS                          |          | 132000        | Hz     | Switching Frequency                                                                   |

| fSmin                       |          | 124000        | Hz     | Minimum Switching Frequency                                                           |

| fSmax                       |          | 140000        | Hz     | Maximum Switching Frequency                                                           |

| IV                          |          | 79.8          | uA     | V pin current                                                                         |

| RV                          |          | 2.00          | M-ohms | Upper V pin resistor                                                                  |

| RV2                         |          | 1.E+12        | M-ohms | Lower V pin resistor                                                                  |

| IFB                         | 165.00   | 165.00        | uA     | FB pin current (85 uA < IFB < 210 uA)                                                 |

| RFB1                        |          | 133.3         | k-ohms | FB pin resistor                                                                       |

| VDS                         |          | 10.00         | V      | LYTSwitch on-state Drain to Source Voltage                                            |

| VD                          |          | 0.50          | v      | Output Winding Diode Forward Voltage Drop (0.5 V for Schottky and 0.8 V for PN diode) |

| VDB                         |          | 0.70          | V      | Bias Winding Diode Forward Voltage Drop                                               |

Figure 6. LYTSwitch-4 Variables Section of the Design Spreadsheet.

Step 2. Enter LYTSwitch-4 Variables (Device Size, Current Limit Mode, R Pin Resistor, V Pin Resistor ( $R_v$ ), FEEDBACK Pin Current  $I_{FB}$ , Drain to Source Voltage ( $V_{DS}$ ), Output Forward Voltage ( $V_D$ ), and Bias Diode Forward Voltage ( $V_{DB}$ )

**Device Selection [B18] and Current Limit Mode [B19]** Select a LYTSwitch-4 device based on the output power using Table 4 for guidance.

For thermally challenging designs, e.g. incandescent lamp replacement, where either the ambient temperature local to the LYTSwitch-4 device is high and/or there is minimal space for heat sinking use the minimum output power column and select the reduced current limit mode by entering RED (Reduced).

For open frame designs or designs where space is available for heat sinking then select from the maximum output power column and select the full current limit mode by entering FULL. stress equals the peak of the AC line voltage so an equivalent rating of 250 V is recommended for low-line input.

Care should be taken when placing the VOLTAGE MONITOR pin resistor(s) on the PCB to avoid noise coupling from the DRAIN node. In designs where encapsulation (potting) is used leakage currents and noise coupling may cause changes in VOLTAGE MONITOR pin current post potting. This effect can be minimized again by careful layout and/or the addition of a 100 nF capacitor and parallel 5.6 V Zener diode connected from the VOLTAGE MONITOR pin to SOURCE pin. Place the capacitor as close to the device as possible and return directly to the SOURCE pin rather than via any other source connected nodes.

#### **REFERENCE** Pin Resistor Value

This component is not included in the design spreadsheet as it is selected from one of two values. The value of the REFERENCE pin resistor is determined based on whether TRIAC dimming is

required. For TRIAC dimming select a value 49.9 k $\Omega$  and for non (TRIAC) dimming 24.9 k $\Omega$ . When configured for dimming the jitter is disabled in deep dimming and line compensation of output current reduced which increases the dimming range. In the non-dimming configuration the line compensation of the output current maintain tight regulation across the input voltage range.

### FEEDBACK Pin Current, $I_{FB}$ , $\mu A$ (Optional)

If left blank a calculated value is used. The calculation depends on the value of the REFERENCE pin resistor (dimming or nondimming configuration) and the value of  $V_{OR}$ . I<sub>FR</sub> is used to regulate the output current and must be in the range of 85  $\mu$ A to 210  $\mu$ A under normal operating conditions including variation in the LED string voltage. Therefore to maximize the allowable output voltage variation and give smallest output current variation a value of 150  $\mu$ A is ideal allowing an LED string voltage variation of up to 2:1, (V<sub>O(MAX)</sub>:V<sub>O(MN)</sub>). In practice most designs have a smaller output voltage variation and any value in the range 110  $\mu$ A to 190  $\mu$ A is acceptable.

### Feedback Resistor Value, $R_{_{FB1}}$ , $k\Omega$

This is the calculated value for the resistor connected to the

| KEY DESIGN PARAMETERS |        |        |    |                                                             |

|-----------------------|--------|--------|----|-------------------------------------------------------------|

| KP                    | 0.87   | 0.87   |    | Ripple to Peak Current Ratio (For PF > 0.9, 0.4 < KP < 0.9) |

| LP                    |        | 373    | uH | Primary Inductance                                          |

| VOR                   | 102.00 | 102.00 | V  | Reflected Output Voltage.                                   |

| Expected IO (average) |        | 0.721  | A  | Expected Average Output Current                             |

| KP_VNOM               |        | 0.83   |    | Expected ripple current ratio at VACNOM (115VAC)            |

| TON_MIN               |        | 2.02   | us | Minimum on time at maximum AC input voltage                 |

| PCLAMP                |        | 0.21   | W  | Estimated dissipation in primary clamp                      |

Figure 7. Key Design Variables Section of the Design Spreadsheet.

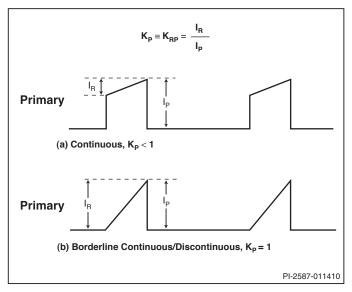

Figure 8. Continuous Conduction Mode Current Waveform (K\_p<1) Showing Definition of K\_p

FEEDBACK pin from the bias winding output to give the value of  $\rm I_{\rm FB}$  at the nominal output voltage (V\_o).

# LYTSwitch-4 Device ON-State Drain to Source Voltage, $V_{ps}$ , V (Optional)

This parameter is the average ON-state voltage developed across the DRAIN and SOURCE pins of LYTSwitch-4. By default, if the grey override cell is left empty, a value of 10 V is assumed. Use the default value if no better data is available.

# Output Diode Forward Voltage Drop, V<sub>D</sub>, V

Enter the average forward drop for the output diode used. A value of 0.5 V is recommended for a Schottky diode and 0.8 V for a PN Ultrafast diode.

# Bias Winding Forward Voltage Drop, $V_{\rm p}$ , V

Enter the average forward drop for the bias winding output diode. Use 0.7 V for a PN diode.

| Input Current Harmonic Analysis |         |       |    |     |

|---------------------------------|---------|-------|----|-----|

|                                 | Max     |       |    |     |

| Harmonic                        | Current | Limit |    | N/A |

| 1st Harmonic                    | 277.78  | N/A   | mA | N/A |

| 3rd Harmonic                    | 15.65   | N/A   | mA | N/A |

| 5th Harmonic                    | 6.74    | N/A   | mA | N/A |

| 7th Harmonic                    | 4.13    | N/A   | mA | N/A |

| 9th Harmonic                    | 2.68    | N/A   | mA | N/A |

| 11th Harmonic                   | 1.65    | N/A   | mA | N/A |

| 13th Harmonic                   | 1.00    | N/A   | mA | N/A |

| 15th Harmonic                   | 0.69    | N/A   | mA | N/A |

|                                 |         |       |    |     |

| THD                             | 17.6    | %     |    | N/A |

Figure 9. Input Current Harmonic Analysis (THD Estimate) of the Design Spreadsheet Section.

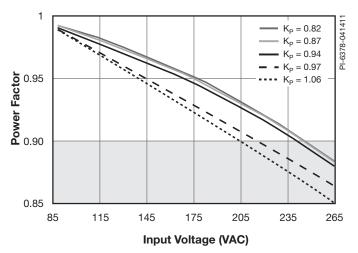

Figure 10. Illustration of the Impact of the Design Parameter  $K_{p}$  on PF.

# Step 3. Enter Key Design Variables: Ripple to Peak Current Ratio (K<sub>p</sub>), Reflected Output Voltage (V<sub>or</sub>)

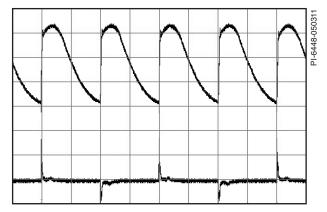

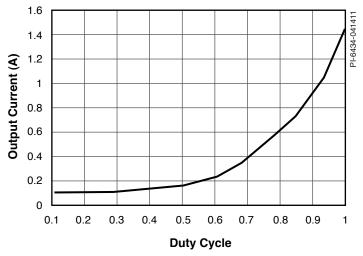

#### Ripple to Peak Current Ratio (K<sub>P</sub>)

Figure 10 shows K<sub>p</sub> < 1, indicating continuous conduction mode, K<sub>p</sub> is the ratio of ripple to peak primary current. LYTSwitch-4 devices require that the design operates in continuous conduction mode to achieve high power factor (PF) and low Total Harmonic Distortions (THD). The recommended range for the value of K<sub>p</sub> is 0.4  $\leq$  KP  $\leq$  0.9. For reference a K<sub>p</sub> value of <0.7 gives a PF >0.95 and THD <20% while a design with a K<sub>p</sub> of 0.9 gives PF >0.9 with THD <30%. At lower power levels higher K<sub>p</sub> values may be used to trade smaller transformer core size against lower

PF and efficiency. By default a value of 0.8 for PO  $\leq\!\!25$  W and 0.4 for P<sub>o</sub>  $>\!\!25$  W is used. For reference Figure 10 shows the measured effect of K<sub>p</sub> on PF in a low-line input, 28 V, 14 W output design.

The goal in selecting the value of K<sub>p</sub> is to use the highest value that still meets the PF, THD and harmonic current specifications. Higher values of K<sub>p</sub> minimize the transformer size and number of turns. For designs less than 25 W input power start with a K<sub>p</sub> value of 1.1. This typically gives PF <0.9, THD <30% and class C (class D limits) compliance. If performance is unacceptable then iterate the design with a lower value for K<sub>p</sub>. For designs above 25 W and where class C compliance uses class C limits is required start with a K<sub>p</sub> value of 0.5. If class C harmonics compliance is not required then use a K<sub>p</sub> value of 1.1. Odd input current harmonics and total harmonics distortion (THD) are automatically calculated in the spreadsheet as shown in Figure 9.

# Reflected Output Voltage, V<sub>OR</sub> (V)

This parameter is the secondary winding voltage during diode conduction, reflected back to the primary through the turns ratio of the transformer. Effectively  $V_{OR}$  is the parameter that sets the turns ratio of the transformer. The default value is 80 V; however the target range for  $V_{OR}$  is between 65 V and 135 V, provided that no warnings in the spreadsheet are triggered. For design optimization purposes, the following trade-offs should be considered:

Higher values of V<sub>OR</sub> (with low values of K<sub>P</sub>) typically requires a larger core size due to the increased primary inductance and number of primary turns.

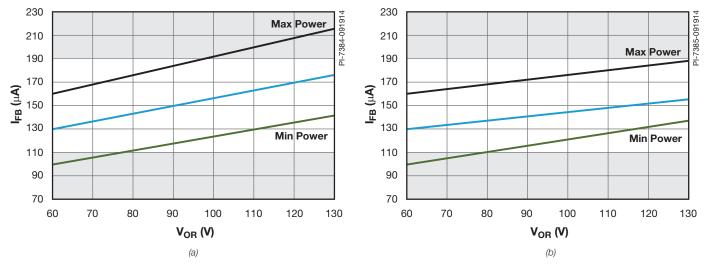

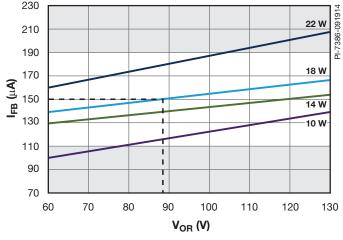

Figure 11. V<sub>np</sub> Selection Curves for Designs using a 2 MΩ (100/115 VAC) (a) and 4 MΩ (230 VAC) (b) VOLTAGE MONITOR Pin Resistor Values.

Figure 12. Example of Selecting V<sub>OR</sub> for a Low Line Input, 14 W Design using

- 2. Higher values of V<sub>OB</sub> reduces the output diode voltage stress. For  $V_{O(MAX)}$  values below ~18 V this allows a Schottky output diode to be selected for lower losses and higher efficiency.

- 3. Higher values of  $V_{OB}$  reduces the maximum power capability of a given LYTSwitch-4 device.

the upper and lower lines with the minimum and maximum power levels from the device data sheet power table. For the LYT4324E the maximum power table value in a high-line only design is 22 W. The minimum is 10 W. Therefore the middle line can be calculated as 16 W. Draw a parallel line between the existing lines on the chart representing the output power required, 17.5 W in this case. Then find the intersection between the 18 W power line and desired value of  $\rm I_{\tiny FR}$  , with a value of 150  $\mu$ A being ideal. In this example the intersection indicated a value for  $V_{OB}$  of 88 V.

### Primary Inductance, $L_{p}$ ( $\mu$ H)

This is the calculated nominal value of primary inductance for the transformer. Designs using LYTSwitch-4 are insensitive to variations in the value of  $L_{\!\scriptscriptstyle P}$  in terms of output current and power delivery with the limitation being that the design maintains operation in continuous conduction mode. A tolerance of ±10% is typical when specifying the design to a transformer vendor.

# Expected Average Output Current, Expected I<sub>O(AVERAGE)</sub> (A)

The calculated average output current, for a valid design this should match specified output current I

# Ripple to Peak Current Ratio at VAC\_{\_{MAX}}, (KP\_{\_{VAC(MAX)}}) This is the calculated value of K\_p at the peak of the maximum

| Core Type   | RM8/I   | RM8/I   |        | Core Size                                                             |

|-------------|---------|---------|--------|-----------------------------------------------------------------------|

|             | FUVIO/I | FUVIO/1 |        |                                                                       |

| Custom Core |         |         |        | Enter custom core part number                                         |

| AE          |         | 0.63    | cm^2   | Core Effective Cross Sectional Area                                   |

| LE          |         | 3.84    | cm     | Core Effective Path Length                                            |

| AL          |         | 3000    | nH/T^2 | Ungapped Core Effective Inductance                                    |

| BW          |         | 8.6     | mm     | Bobbin Physical Winding Width                                         |

| М           |         | 0.00    | mm     | Safety Margin Width (Half the Primary to Secondary Creepage Distance) |

| L           | 2       | 2       |        | Number of Primary Layers                                              |

| NS          | 16      | 16      |        | Number of Secondary Turns                                             |

Figure 13. Transformer Variables Section of the Design Spreadsheet.

Optimal selection of the  $V_{OR}$  value depends on the specific application and is based on a compromise between the factors mentioned above. Figure 11 (a) & (b) may be used as a guide and provides an initial value based on the value of the VOLTAGE MONITOR pin resistor and the output power. The upper line represents the maximum and lower line the minimum output power from the selected LYTSwitch-4 device as shown in the data sheet power table. The middle line is the mid point between these two power levels. The unshaded region is the recommended range for the feedback current  $I_{FB}$ .

An example of using these selection curves for a 18 W, lowline, LYT4324E design is shown in Figure 12. Start by labeling

input voltage ( $V_{\text{AC(MAX)}}$ ). This value should remain below 1.12 to ensure a PF of <0.9 at nominal AC input.

Minimum On Time at VAC  $_{\mbox{(MAX)}}, t_{\mbox{on(MIN)}}$  (µs) This is the calculated minimum on time of the internal MOSFET at the peak of  $V_{\scriptscriptstyle AC(MAX)}\!.$  This value is should be greater than the minimum device on time of 1.5 µs.

# Clamp Dissipation, P<sub>CLAMP</sub> (W)

This is the calculated dissipation in the primary clamp. The calculation includes the effect of the variation in instantaneous dissipation over each AC half-cycle.

# Step 4 – Select Transformer Core and Bobbin Based on Output Power and Enter A<sub>E</sub>, L<sub>E</sub>, A<sub>L</sub>, BW, M, L, N<sub>S</sub>

Core effective cross-sectional area,  $A_E$  (cm<sup>2</sup>) Core effective path length,  $L_E$  (cm) Core ungapped effective inductance,  $A_L$  (nH/turn<sup>2</sup>), Bobbin width, BW (mm) Tape margin width equal to half the total margin, M (mm) Primary Layers, L Secondary Turns, N<sub>e</sub>

# Core Type

If the core type cell is left as the default of Auto, the spreadsheet will default to the smallest commonly available core suitable for the output power specified. The entire list of cores available can be selected from the drop down list in the tool bar of the PIXIs design software.

The grey override cells can be used to enter the core and bobbin parameters directly. This is useful if a core is selected that is not on the list, or the specified core or bobbin information differs from that referenced by the spreadsheet.

Note some core and bobbin types may not meet safety spacing requirements (e.g. RM or smaller EE sizes). In these cases it is common to use a triple insulated secondary winding terminated as flying leads (rather than to the bobbin pins). This allows safety creepage and clearance distances to be met and saves PCB board area by eliminating the need for a bobbin with increased spacing.

# Safety Margin, M (mm)

For designs that require safety isolation between primary and secondary but do not use triple-insulated wire, the width of the safety margin to be used on each side of the bobbin should be entered here. For universal input designs, a total margin of 6.4 mm would be required, and a value of 3.2 mm would be entered into the spreadsheet. For low-line only input designs (100/115/127 VAC) a total margin of 4 mm would be required and 2 mm entered into the spreadsheet. For vertical bobbins

the margin may not be symmetrical. However, if a total margin of 6.2 mm were required, then 3.1 mm would still be entered even if the physical margin were only on one side of the bobbin.

For designs using triple insulated wire, it may still be necessary to enter a small margin in order to meet the required safety creepage distances.

Many bobbins exist for any core size and each will have different mechanical spacing. Refer to the bobbin data sheet or seek guidance from your safety expert or transformer vendor to determine what specific margin is required.

As the margin reduces the available area for the windings, the margin format described above may not be suitable for small core sizes. If after entering the margin, more than 3 primary layers (L) are required, it is suggested that either a larger core be selected or switch to a zero margin design approach using triple insulated wire.

# Primary Layers, L

Primary layers should be in the range of 1 < L < 3, with a default value of 3. This provides a good compromise between winding losses and leakage inductance for a transformer core size appropriate for the output power. Three layers also results in lower capacitance hence improving efficiency, especially at higher input voltages. The lower limit on the value for L is set by the primary winding current density limits (circular mils per amp or CMA). CMA has a strong influence on the winding losses and therefore transformer temperature rise and efficiency. CMA values as low as 200 for designs <10 W scaling linearly to 600 at >75 W are good design targets for convection cooled designs. For designs where the driver will be encapsulated for thermal management a lower value of CMA may be acceptable. Whether or not an encapsulate is used verification of the winding temperatures (using non-ferrous T type thermocouples) is recommended. This is achieved by embedding a thermocouple into the transformer between two of the insulation tape layers that are present between the primary and secondary windings during construction. Most designs will fall into

| TRANSFORMER PRIMARY DESIGN PARAMETE | ERS  |           |                                                                 |

|-------------------------------------|------|-----------|-----------------------------------------------------------------|

| LP                                  | 373  | uH        | Primary Inductance                                              |

| LP_TOL                              | 10   |           | Tolerance of primary inductance                                 |

| NP                                  | 45   |           | Primary Winding Number of Turns                                 |

| NB                                  | 11   |           | Bias Winding Number of Turns                                    |

| ALG                                 | 187  | nH/T^2    | Gapped Core Effective Inductance                                |

| BM                                  | 2013 | Gauss     | Maximum Flux Density at PO, VMIN (BM<3100)                      |

| BP                                  | 3619 | Gauss     | Peak Flux Density (BP<3700)                                     |

| BAC                                 | 876  | Gauss     | AC Flux Density for Core Loss Curves (0.5 X Peak to Peak)       |

| ur                                  | 1455 |           | Relative Permeability of Ungapped Core                          |

| LG                                  | 0.40 | mm        | Gap Length (Lg > 0.1 mm)                                        |

| BWE                                 | 17.2 | mm        | Effective Bobbin Width                                          |

| OD                                  | 0.38 | mm        | Maximum Primary Wire Diameter including insulation              |

| INS                                 | 0.06 | mm        | Estimated Total Insulation Thickness (= 2 * film thickness)     |

| DIA                                 | 0.33 | mm        | Bare conductor diameter                                         |

| AWG                                 | 28   | AWG       | Primary Wire Gauge (Rounded to next smaller standard AWG value) |

| СМ                                  | 161  | Cmils     | Bare conductor effective area in circular mils                  |

| CMA                                 | 331  | Cmils/Amp | Primary Winding Current Capacity (200 < CMA < 600)              |

Figure 14. Transformer Primary Design Parameters Section of the Design Spreadsheet

| TRANSFORMER SECONDARY DESIGN PARAMETERS (SINGLE OUTPUT EQUIVALENT) |      |       |                                                                     |  |  |  |

|--------------------------------------------------------------------|------|-------|---------------------------------------------------------------------|--|--|--|

| Lumped parameters                                                  |      |       |                                                                     |  |  |  |

| ISP                                                                | 4.24 | A     | Peak Secondary Current                                              |  |  |  |

| ISRMS                                                              | 1.32 | A     | Secondary RMS Current                                               |  |  |  |

| IRIPPLE                                                            | 1.12 | A     | Output Capacitor RMS Ripple Current                                 |  |  |  |

| CMS                                                                | 264  | Cmils | Secondary Bare Conductor minimum circular mils                      |  |  |  |

| AWGS                                                               | 25   | AWG   | Secondary Wire Gauge (Rounded up to next larger standard AWG value) |  |  |  |

| DIAS                                                               | 0.46 | mm    | Secondary Minimum Bare Conductor Diameter                           |  |  |  |

| ODS                                                                | 0.54 | mm    | Secondary Maximum Outside Diameter for Triple Insulated Wire        |  |  |  |

Figure 15. Transformer Secondary Design Parameters Section on

| VOLTAGE STRESS PARAMETERS |     |   |                                                                                     |

|---------------------------|-----|---|-------------------------------------------------------------------------------------|

|                           |     |   | Estimated Maximum Drain Voltage assuming maximum LED string voltage (Includes       |

| VDRAIN                    | 397 | V | Effect of Leakage Inductance)                                                       |

|                           |     |   | Output Rectifier Maximum Peak Inverse Voltage (calculated at VOVP, excludes leakage |

| PIVS                      | 110 | V | inductance spike)                                                                   |

|                           |     |   | Bias Rectifier Maximum Peak Inverse Voltage (calculated at VOVP, excludes leakage   |

| PIVB                      | 77  | V | inductance spike)                                                                   |

Figure 16. Voltage Stress Parameters Section of the Design Spreadsheet

insulation class A or class B limiting maximum winding temperatures (at maximum external ambient) to 105 °C and 130 °C respectively.

Designs with more than 3 layers are possible, but the increased leakage inductance and issues associated with the physical fit of the windings should be considered. A split primary construction may be helpful for designs where leakage inductance clamp dissipation is too high and providing there is sufficient winding window. In a sandwich construction half of the primary winding is placed on either side of the secondary (and bias) windings. Sandwich construction is recommended for all design >20 W.

# Secondary Turns, N<sub>s</sub>

If the grey override cell is left blank, the minimum number of secondary turns is calculated such that the maximum operating flux density  $B_M$  is kept below the recommended maximum of 3100 Gauss (310 mT). In general, it is not necessary to enter a number in the override cell except in designs where a lower operating flux density is desired (see the explanation of  $B_M$  limits).

# Step 5 – Iterate Transformer Design / Generate Prototype

Iterate the design making sure that no warnings are displayed. Any parameters outside the recommended range of values can be corrected by following the guidance given in the right hand column. Once all warning and errors have been addressed click on the Transformer Parameter and Transformer Construction tabs to obtain detailed transformer specification and construction details. These can be used to either construct the transformer in house or send to an external magnetic vendor.

The key transformer electrical parameters are:

#### Primary Inductance, $L_{P}$ ( $\mu$ H)

This is the target nominal primary inductance of the transformer.

# Number of Primary Turns, N<sub>P</sub>

This is the number of turns for the main primary winding.

# Gapped Core Effective Inductance, $A_{LG}$ (nH/T<sup>2</sup>)

Used by the transformer vendor to specify the core center leg air gap. This is the value of inductance obtained (in nH) for the number of turns placed around the core squared.

### Maximum Operating Flux Density, B<sub>M</sub> (Gauss)

A maximum value of 3100 Gauss during normal operation is recommended. This prevents core saturation during start-up or output short-circuit

#### Peak Flux Density, B<sub>P</sub> (Gauss)

A maximum value of 3700 Gauss is recommended to limit the maximum flux density under start-up and output short-circuit conditions. In these cases the output voltage is low and little reset of the transformer core occurs during the MOSFET off-time. This can allow the transformer flux density to increase during the next and subsequent cycles (stair casing) until the core saturates. A value of 3700 Gauss, calculated at the maximum device current limit, together with the built-in protection features of LYTSwitch-4 devices, provides sufficient margin to prevent core saturation under start-up or output short-circuit conditions.

This calculation assumes worst-case current limit and nominal inductance values and accounts for high ambient temperatures as this reduces the saturation flux density of ferrite materials. It is important to verify that core saturation does not occur at maximum ambient temperature under start-up and overload conditions just prior to loss of regulation.

#### Maximum Primary Wire Diameter, OD (mm)

This is the calculated maximum wire size diameter that will allow the number of primary turns ( $N_p$ ) to fit into the specified bobbin width (BW) with the specified number of layers (L).

The other factors automatically calculated by the spreadsheet include:

Estimated total insulation thickness, INS (mm) Primary wire size, DIA: (mm) Primary wire gauge, AWG

Number of primary layers, L Estimated core center leg gap length:  $L_g$ : (mm) Number of secondary turns,  $N_s$  Secondary wire size, DIA<sub>s</sub>: (mm) Secondary wire gauge, AWG

# Step 6 - Selection of LYTSwitch-4 External Components

The schematic shown in Figure 1 shows the external components for a typical LYTSwitch-4 power supply design. Each of these is dealt with in the relevant section below.

# **BYPASS Pin Capacitor (C8)**

The BYPASS pin is both the supply rail for the IC and sets the operating mode between reduced and full power. For reduced power mode a 47  $\mu$ F capacitor should be selected and for full power a 4.7  $\mu$ F capacitor based on the selection entered into the design spreadsheet. Either ceramic or electrolytic types may be used with a voltage rating of 10 V or above and tolerance plus temperature variation of less than ±50%. Larger variation may cause the 47  $\mu$ F capacitor to be incorrectly detected as a 4.7  $\mu$ F value.

# **REFERENCE (R) Pin Resistor (R14)**

This pin determines the operating mode between dimming and non-dimming operation. LYTSwitch-4 low-line family for dimming operation at 49.9 k $\Omega$  1% part and for non-dimming operation a 24.9 k $\Omega$  1% part should be used. While LYTSwitch-4 high-line family only 24.9 k $\Omega$  1% part should be used be it dimming and non-dimming operation. Resistors with 1% tolerance (or better) should be used as variations in the resistor value directly impacts the supply output current and VOLTAGE MONITOR pin thresholds for line OV.

# VOLTAGE MONITOR (V) Pin Resistor(s) (R<sub>v1</sub> and R<sub>v2</sub>)

The initial value of the total resistance connected from the VOLTAGE MONITOR pin to the DC bus is provided in the design spreadsheet as parameter  $R_{v_1}$ . Resistor  $R_{v_2}$  is connected from the VOLTAGE MONITOR pin to SOURCE, typically only present in non-dimming designs to provide constant output current vs. line voltage. Both resistors should have 1% tolerance (or better) to provide unit to unit matching of dimming characteristics. A value for  $R_{v_2}$  of >10  $M\Omega$  indicates that it is not required as its effect will be negligible. In Figure 1  $R_{v_1}$  is R10 while  $R_{v_2}$  is not shown as it was not required for this design.

# External Bias Current (R17, D5)

Resistor R5 provides the operating current for U1 during normal operation. The inclusion of external bias is recommended even though, with the exception of the LYT-4XX1 smallest device, LYTSwitch-4 devices can operate without any external bias. Providing an external bias reduces the device dissipation and allows operation to smaller conduction angles when used with phase angle dimmers. The design goal is to provide a current into the BP equal to  $I_{CD1(MAX)}$  under worst-case conditions. Worst-case usually occurs at  $V_{O(MIN)}$  and lowest output current (due to dimming).

As an initial starting value or dimming designs the value of R17 should be selected to provide approximately 5 mA into the BYPASS pin at the nominal output voltage ( $V_o$ ) according to the expression,

$$R5 = \frac{V_B - V_{BP}}{3 \times I_{CD1(MAX)}}$$

where  $V_{\rm B}$  is the bias voltage from the design spreadsheet and  $V_{\rm BP}$  is the BYPASS pin voltage (5.9  $V_{\rm TYP}$ ) and  $I_{\rm CD1(MAX)}$  is the IC supply current from the device data sheet. The factor of 3 provides adequate margin due to variations in the bias voltage due to LED string (output) voltage, especially the reduction in the value of  $V_{\rm B}$  that occurs during dimming.

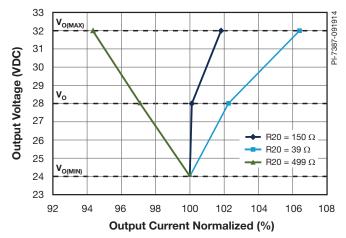

Figure 17. Effect of R20 (Bias Winding Filter Resistor) on Output Current Regulation vs LED String Voltage (±15%).

For non dimming designs the factor of 3 can be omitted. Dissipation in R20 is <50 mW and tolerance is not critical (5% is acceptable).

Diode D5 can be any small signal diode with a voltage rating above 10 V (e.g. 1N4148, BAV16 etc). It is included to isolate the BYPASS pin from the bias winding capacitor (C9) to prevent increased start-up delay and misdetection of the value of the bypass capacitor.

# Bias Diode (D6)

The primary referenced auxiliary winding on the transformer is rectified and filtered to create a bias supply that provides both the operating current into the BYPASS pin and feedback information into the FEEDBACK pin. The rectifier diode (D6) can be any fast or ultrafast recovery type with a voltage rating above the value given in the design spreadsheet (PIVB), typically >200 V, and current rating >200 mA. The 1N4936 and UF4004 or SMD equivalents are good examples.

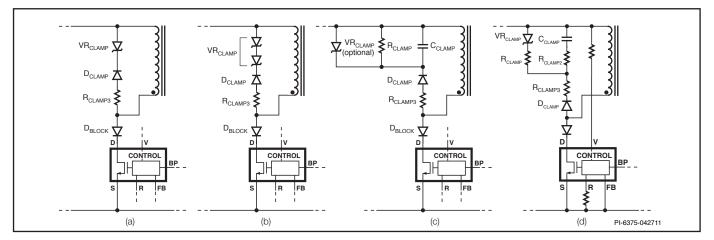

Figure 18. Recommended Clamp Configurations for LYTSwitch-4 Designs. (a) Zener Clamp, (b) Zener Clamp with Series Connected Zeners for Higher Power, (c) RCD / RCD+Z Clamp, (d) Zener Bleed Clamp.

| P <sub>o</sub> (W) | Reference<br>Document | Configuration | D <sub>BLOCK</sub> | VR <sub>CLAMP</sub><br>(V) |        | R <sub>clamp</sub><br>(kΩ) | R <sub>clamp2</sub><br>(Ω) | R <sub>clamp3</sub><br>(Ω) | C <sub>CLAMP</sub><br>(pF) |

|--------------------|-----------------------|---------------|--------------------|----------------------------|--------|----------------------------|----------------------------|----------------------------|----------------------------|

| 7                  | RDR-193               | A             | ES1D               | P6KE200                    | UF4007 | -                          | -                          | -                          | -                          |

| 6.9                | DER-269               | С             | US1D               | -                          | RS1J   | 100                        | -                          | 100                        | 1000                       |

| 8                  | DER-264               | С             | US1D               | -                          | RS1J   | 50                         | -                          | 100                        | 1000                       |

| 14                 | RDR-195               | A             | UF4006             | P6KE200                    | UF4007 | -                          | -                          | -                          | -                          |

| 15                 | DER-256               | С             | MUR120             | -                          | FR107  | 82                         | -                          | 100                        | 1000                       |

| 15                 | DER-278               | A             | UF4004             | P6KE200                    | UF4007 | -                          | -                          | -                          | -                          |

Table 5. Example Clamp Component Values for LinkSwitch-PH Designs (applicable to LYTSwitch designs).

# Filter Resistor (R20) and Capacitor (C9)

These two components form a low pass filter (pole). The corner frequency (1/2 ×  $\pi$  × R20 × C9) should be where f<sub>L</sub> is the minimum line frequency to prevent line frequency ripple modulating the FEEDBACK pin. A corner frequency of 50 Hz results in a power factor above 0.9 at 230 VAC input. If lower power factor is acceptable the corner frequency can be increased to allow the use of a lower value capacitor. The value of R20 should be in the range of 47  $\Omega$  to 200  $\Omega$  (5% tolerance). Making the value too high results in a reduction in the bias voltage which can reduce the minimum conduction angle at which the supply will operate. Making the value too small results in the value of C9 increasing which is undesirable due to board space constraints. Capacitor C9 should have a voltage rating above the value of V<sub>B</sub> × (V<sub>O(MAX</sub>) / V<sub>o</sub>) and can be either an electrolytic or ceramic type.

Resistor R20 also optimizes output current regulation with changes in output voltage. Figure 17 shows the effect of changing R20 over a 10:1 range. It can be seen that a value of 150  $\Omega$  in this case gave the best output current regulation as the output voltage was varied  $\pm 15\%$ .

#### **Bleed Resistor (R19)**

This resistor provides an addition load on the bias supply to prevent the voltage from peak charging due to the effects of transformer leaking inductance. Select the value (5% tolerance) to generate a current of ~2 mA at the bias voltage (V\_R).

#### Feedback Resistor (R18)

For the first prototype use the value provided in the design spreadsheet (R<sub>FB1</sub>). As this resistor directly impacts the output regulation it should have a 1% tolerance.

#### Peak Detector (D2, R9 and C6)

This network is used to provide a DC voltage from which a current is fed into the V pin of the LYTSwitch-4 device.

Diode D2 allows C6 to charge to the peak of the incoming rectified AC. Resistor R9 provides a discharge path to allow the voltage across C6 to track changes in the incoming AC. The value of C6 should be  $\geq$ 100 nF for a PF of >0.9. Larger values (up to 1 µF) further increase the achievable PF up to 0.99. Values above 1 µF provide only incremental improvement but do provide additional filtering during differential line surges, reducing the peak drain voltage. A voltage rating of >1.41 × VAC<sub>MAX</sub> is required and both film, ceramic or electrolytic types may be used. Resistor R9 should be selected such that R9 × C6 >80 ms so that the voltage across C6 is essentially constant over one AC half cycle. A voltage rating of >1.41 × VAC<sub>MAX</sub> is recommended. A standard 1N4007 plastic rectifier is recommended for D1.

# Step 7 – Selection of Primary Clamp Components (R15, C7 and D3)

Several different clamp configurations are shown in Figure 18. Diode D<sub>BLOCK</sub> (D3 in Figure 1) prevents current flow occurring from source to drain during the period of each AC half-cycle where the rectified AC voltage is below the reflected output voltage ( $V_{OR}$ ) of the design. The diode should be an ultrafast type and have a current rating above the average drain current ( $I_{AVG}$ ) and voltage rating of >1.2 ×  $V_{OR}$  × ( $V_{O(MAX)}$  /  $V_{O}$ ). Good choices for this components include the US1J (1 A) and UF5402 (3 A).

When the internal power MOSFET turns off, leakage inductance induces a voltage spike on the drain. To limit this voltage to below the 725 V BV<sub>DSS</sub> rating of the internal MOSFET a clamp is required across the primary of the transformer. The clamp both limits the drain voltage and dissipates the leakage inductance energy. Clamp selection and design is similar to that of a standard flyback converter however the absence of bulk storage capacitance after the rectifier (to give high power factor) requires additional consideration.

The peak voltage on the drain is a function of the value of the input voltage,  $V_{_{\rm OB}}$  and the clamp voltage.

During each AC half-cycle, the primary peak current varies to provide an envelope that follows the AC voltage (giving high power factor). As the leakage energy is a function of the peak primary current this also varies during each AC half-cycle ( $E_{LEAK} = 0.5 \times L_{LEAK} \times IP^2$ ). Peak leakage energy occurs at the peak of the rectified input AC corresponding to the design spreadsheet value of IP and it is at this point where the maximum peak drain voltage occurs.

The clamp must therefore be designed to provide sufficient drain voltage margin at the peak of the maximum AC input voltage ( $1.41 \times VAC_{MAX}$ ) and the maximum output voltage. In addition the clamp voltage must also remain significantly above the value of V<sub>OR</sub> to minimize the amount of magnetizing energy (the energy that is stored in the transformer during the switch on time) being dissipated in the clamp.

The Zener or Zener Bleed configurations are preferred for high efficiency because the clamp voltage does not reduce below a fixed value (defined by the voltage of the Zener) irrespective of the value of  $E_{LEAK}$ . In comparison an RCD clamp used in this design, least expensive clamp has a clamping voltage that varies with the value of  $E_{LEAK}$ , reducing with the value of  $E_{LEAK}$ . As the clamp voltage reduces, towards the value of  $V_{OR}$ , proportionally more energy is dissipated in the clamp and less is delivered to the output thereby reducing efficiency.

The Zener configuration (Figure 18a) is the simplest to design, gives the highest efficiency across variations in output voltage and requires the fewest components but may have higher EMI generation due to higher dv/dt and di/dt.

The Zener Bleed configuration provides the lower EMI generation of an RCD clamp but has a defined minimum clamp voltage. The operation is similar to the RCD clamp. When the primary switch turns off, the leakage inductance energy charges  $C_{_{\rm CLAMP}}$  to above the voltage rating of VR\_{\_{\rm CLAMP}}. For the remainder of the switching period  $C_{_{\rm CLAMP}}$  is discharged via  $R_{_{\rm CLAMP}}$  and VR\_{\_{\rm CLAMP}} ready for the next turn-off event. The addition of VR\_{\_{\rm CLAMP}} in series with  $R_{_{\rm CLAMP}}$  ensures that the voltage across  $C_{_{\rm CLAMP}}$  cannot discharge to below the voltage rating of VR\_{\_{\rm CLAMP}}. Dissipation is shared between VR\_{\_{\rm CLAMP}} and  $R_{_{\rm CLAMP}}$  with the recommended voltage rating of VR\_{\_{\rm CLAMP}} being ~10% higher than the V\_{\_{\rm OR}} of the design.

The RCD configuration (Figure 18c with VR<sub>CLAMP</sub> omitted) is attractive because of low EMI generation, low-cost and scalability for higher power designs. The higher dissipation may be accommodated by sizing the power rating of R<sub>CLAMP</sub> or using multiple resistors in parallel. However the RCD clamp requires more careful design as the clamping voltage varies with output voltage and peak drain current. This requires that the maximum clamp voltage is set at  $V_{O(MAX)}$  and therefore results in lower efficiency at the nominal output voltage (V<sub>O</sub>).

By adding a Zener to the RCD configuration (Figure 18c with VR<sub>CLAMP</sub> present) to form the RCD+Z provides a good compromise between the fixed clamping voltage of a Zener and high power capability of the RCD. The Zener provides a fixed voltage clamp during transients (start-up or output short-circuit) but during normal operation the RC network clamps the peak drain voltage.

Zener diode peak current for configuration 16a and 16b is typically 0.6 to  $0.8 \times I_p$  and therefore transient suppressor diodes (TVS) are recommended. The P4KExxxA (1 W), P6KExxxA (5 W) and 1.5KExxxA (6.5 W) are good examples (where xxx represents the voltage rating and A indicates uni-directional.

For the RCD+Z and Zener Bleed configurations (Figures 16c and 16d) the peak Zener currents are significantly lower and standard 1-2 W Zener diode may be selected such as the BZY97Cxxx.

For high-power capability multiple Zener diodes may be placed in series (as shown in Figure 18b) with the overall voltage being equal to the desired clamping voltage. This is typically only required in output powers above 50 W based on Zener temperature rise.

For Figure 18 configurations (a), (b) and (c) a voltage rating of 200 V is recommended for VR<sub>CLAMP</sub> but this can be lowered to provide additional drain voltage margin providing the value of VR<sub>CLAMP</sub> is >1.4 × V<sub>OR(MAX)</sub>, where V<sub>OR(MAX)</sub> is equal to V<sub>OR</sub> × (V<sub>O(MAX)</sub>/V<sub>O</sub>).

Select the power rating of the clamp Zener(s) and/or resistor(s) based on the value for P<sub>CLAMP</sub> given in the Key Design Parameters section of the design spreadsheet. This value represents the average energy dissipated in the clamp over one AC line cycle. Table 4 provides a good starting point for component selection based on output power.

Once a prototype is constructed verify the clamp component temperature to ensure that there is sufficient design margin

when operated inside the final product enclosure (including LED) and highest ambient temperature.

$\rm D_{\rm CLAMP}$  should be a fast or ultrafast type with a reverse recovery time <500 ns. Under no circumstances should a standard recovery rectifier diode be used. The high dissipation that may result during start-up or an output short-circuit can cause failure of the diode.

#### Step 8 – Output Overvoltage (Disconnected Load Protection – Optional) (D8, C15, R22, R27, VR4, C14 and Q2 in Figure 1)

The purpose of this optional functional block is to limit the output voltage should the load (LED string) be disconnected. Without this protection the output voltage will rise to a high value that can cause failure of the output capacitors, the clamp components and the LYTSwitch-4 device. Even in LED retro-fit lamp applications, where disconnection of the LED load is a fault condition and represents product failure, output OVP may still be desirable to protect the supply during the manufacturing process and maintain the output voltage within SELV (safety extra low voltage) safety limits.

During unloaded operation the output voltage will rise, resulting in a proportional rise in the bias winding voltage. Once VR4 conducts and Q2 is biased on the FEEDBACK pin of U1 is pulled to source, initiating auto-restart mode. Once in autorestart the 300 ms (600 ms – High-Line Family) off-time allows the output voltage to discharge via R23.

As soon as the load is reconnected normal operation resumes after the completion of the auto-restart off period. The bias voltage is separately rectified and filtered by D8 and C15 to allow a faster response time than using the voltage across C9. Diode D8 can be any small signal diode with a voltage rating greater that the value given in the design spreadsheet (PIV<sub>p</sub>) and a current rating >150 mA. The value of C15 is not critical, use a 100 nF - 1  $\mu$ F value and voltage rating above the bias voltage if no better data is available. Resistor R22 provides some load across C14 preventing peak charging. Start with a value of 1 k $\Omega$ , 5%.

Select the initial voltage rating of VR4 to be V<sub>OVP</sub> × N<sub>B</sub>/N<sub>S</sub> + 5 V where the value of V<sub>OVP</sub> is given in the Applications Variables section of the design spreadsheet. The 5 V figure compensates for the effects of peak charging and prevents false triggering under normal operation. Parts with power ratings ≤0.5 W and a tolerance of 5% are recommended.

Capacitor C14 provides noise filtering. Select any generic 100 nF, 50 V ceramic capacitor. Resistor R22 defines the current before Q2 is biased on, improving accuracy by operating the Zener closer to its data sheet test current. A value of 330  $\Omega$  to 1 k $\Omega$ , 5% is recommended, giving a Zener current of 0.5 mA to 2 mA. Transistor Q2 can be any small signal NPN transistor (collector voltage is <10 V and currents <1 mA). Once a prototype is constructed adjust the voltage of VR4 to be 5 – 10 V above the measured voltage across C15 at V<sub>O(MAX)</sub> (the maximum LED string voltage). This ensures that Q2 remains

completely off during normal operation, preventing changing the output current.

# Step 9 - Output Diode, Capacitors and Pre-load

# (D7, C11, C12 and R23)

Select an output diode with a current rating of  $\geq$ IO and a voltage rating V<sub>RRM</sub> >PIV<sub>s</sub> where I<sub>o</sub> and PIV<sub>s</sub> are values from the design spreadsheet. A current rating of  $\geq 2 \times I_o$  results in higher efficiency and should be considered where necessary.

Ultrafast ( $t_{\rm RR}$ <150 ns) or Schottky types should be selected. Schottky types will give higher efficiency, especially in lower output voltage designs where the diode forward voltage is a larger proportion of the secondary winding voltage.

Low or very low ESR capacitors should be used. Select the values based on allowable output (LED) current ripple with an initial value = ~1.5  $\mu$ F per mA of output current for ±50% output current ripple. The capacitance value may be split across several capacitors for space reasons. When using low ESR types the ripple current rating of the capacitors is typically much higher than actual ripple current so typically this rating doesn't need to be considered.

Larger values of output capacitance reduces the output ripple and improves dimming range by maintaining feedback into the LYTSwitch-4 device even at very small TRIAC conduction angles.

Output LED ripple currents of  $\leq$ 50% vs. DC have little performance impact, with negligible change in LED efficiency or color temperature.

Either electrolytic or ceramic capacitors may be used. Ceramic capacitors offer longer lifetime than electrolytic types however when used as output capacitors there is less benefit. This is due to the effect on LED operation at end life. Here the reduction in capacitance and increase in ESR results in higher LED ripple current but not outright failure of the driver. Lifetime of electrolytic capacitors is directly affected by operating temperature. However when using low ESR types with sufficient capacitance to limit output current ripple to ≤50% then capacitor self-heating is negligible and the operating temperature is equal to the ambient temperature.

Select the value of the output discharge and pre-load resistor to provide a current of 1.5 mA at the output voltage (R15 =  $V_{\rm o}$  / 1.5 mA).

This resistor causes the output to discharges below the LED string voltage when the AC is removed and therefore ensures the LED extinguish rather than there being a slight glow for several seconds after AC is removed.

# Step 10 – TRIAC Leading Edge Dimmer Compatibility Components

# Working with TRIAC Dimmers

The requirement to provide output dimming with low-cost, TRIAC based, leading edge phase dimmers introduces a number of trade-offs in the design.

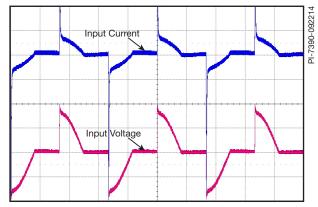

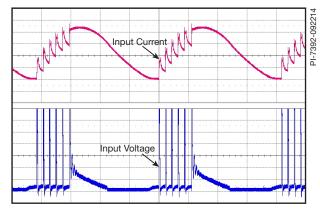

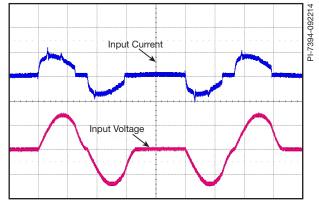

Figure 19. Typical Input Voltage and Current Waveforms for a Leading Edge TRIAC Dimmer Connected to a Driver at 90° Conduction Angle. Upper: AC Current (200 mA / div.), Lower: AC Voltage (200 V / div.)

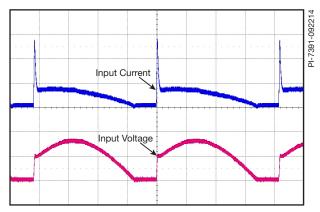

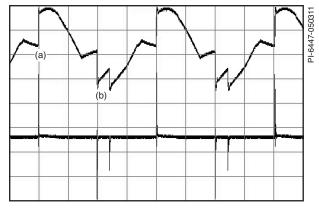

Figure 20. Resultant Waveforms Following Rectification of Typical TRIAC Dimmer Output. Upper: Rectified AC Current (200 mA / div.), Lower: Rectified AC Voltage (200 V / div.)

Figure 21. Example of Phase Angle Dimmer Showing Erratic Firing Following Rectification of Typical TRIAC Dimmer Output. Upper: Rectified AC Voltage (100 V / div.), Lower: Rectified AC Current (0.3 A / div.)

For correct operation incandescent phase angle dimmers typically have a specified minimum load, typically ~40 W for a 230 VAC rated unit. This is to ensure that the current through the internal TRIAC stays above its specified holding current threshold.

Due to the much lower power consumed by LED lighting the input current drawn by the lamp is below the holding current of the TRIAC within the dimmer. The input capacitance of the

driver allows large inrush currents to flow when the TRIAC fires. This then generates input current ringing with the input stage and line inductance which may cause the current to fall below the TRIAC holding current. Both of these mechanisms cause undesirable behavior such as limited dimming range and/or flickering.

To overcome these issues two circuit blocks, damper and bleeder, are incorporated in dimming applications. The drawback of these circuits is increased dissipation and therefore reduced efficiency of the supply.

Figure 19 shows the line voltage and current at the input of a leading edge TRIAC dimmer. In this example, the TRIAC conducts at 90 degrees.

Figure 20 shows the desired rectified bus voltage and current. Figure 21 shows undesired rectified bus voltage and current with the TRIAC turning off prematurely and restarting. This is due to the input current ringing below the holding current of the TRIAC, excited by the initial inrush current.

If the TRIAC is turning off before the end of the half cycle or rapidly turning on and off then a bleeder and damper circuit are required.

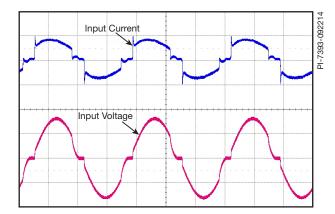

Figure 22. Example of TRIAC Dimer Output Voltage and Current Showing Half-Cycle Dissymmetry Upper: AC Voltage (200 V / div.), Lower: AC Current (1 A / div.)

Figure 23. Example Waveforms Showing Correct TRIAC Operation at Minimum Conduction Angle. Upper: Rectified AC Voltage (100 V / div.), Lower: AC Current (1 A / div.)

In general as power dissipated in the bleeder and damper circuits increases, so does dimmer compatibility.

Initially install a bleeder network across the rectified power bus (R1 and C1 in Figure 1) with initial values of 0.22  $\mu F$  and a total resistance of 510  $\Omega$  and power rating of 2 W.

Reduce the capacitance value to find the minimum acceptable value. Reducing the capacitance value reduces power dissipation and therefore increases efficiency.

If the bleeder circuit does not maintain conduction in the TRIAC on both AC half-cycles, then add a damper. Figure 22 shows a typical waveform where the bleeder circuit alone is not sufficient to maintain correct TRIAC conduction on both AC half-cycles. On positive half-cycles (a) the TRIAC conducts for the full conduction angle but on the negative half-cycle (b) the TRIAC fires twice. In this case a damper is required. The purpose of the damper is to limit the inrush current that flows through the input stage and line inductances as the input capacitance charges. Without limiting this current the input capacitor (C2 in Figure 1) voltage can reach significantly above the peak of the incoming AC voltage which causes the TRIAC current to fall to zero and therefore turn off. This cycle then repeats causing flicker.

For designs with an output power of less than 6 W, a passive damper may be used. Here a simple resistor in series with the AC input. Values in the range of 10  $\Omega$  – 150  $\Omega$  are typical with the upper range being limited by the allowed dissipation / temperature rise and reduction in efficiency. Values below 10  $\Omega$  may also be used but are less effective especially in high AC line input designs.

For higher power designs or if the passive damper is insufficient to prevent incorrect TRIAC operation then an active damper is required. This is typical in high-line applications due to the much larger inrush current that flows when the TRIAC turns on. A low-cost active damper circuit is formed by R6, R29, R28, R8, D10, C3, VR5, Q3 and Q1 in Figure 1. Resistor R8 limits the inrush current and can be a much higher value for better damping than the passive case as they are in circuit for only a fraction of the line cycle. MOSFET Q1 shorts R8 after a delay defined by R16, R29 and C3. The delay is adjusted to give the shortest time that provides acceptable dimmer performance to minimize the dissipation in R8. Figure 23 shows the effect of adding the damper compared to the waveform in Figure 22. Here the TRIAC correctly conducts once each half-cycle. The MOSFET required is a low current, low-cost device available with very low gate current requirements. Maximum dissipation in the resistors of the damper and bleeder occurs at 90 degree TRIAC conduction and therefore thermal testing should be performed under this condition to verify component temperatures. For high-line designs it may be necessary to use a wire wound construction for the active damper resistor to prevent failure. This is due to the high instantaneous power dissipated when AC is first applied. In this case a single resistor is acceptable, for example the CRF series from Vitrohm.