Программирование ПЛИС (FPGA) Xilinx. Языки проектирования ПЛИС и СнК.

«Программирование» ПЛИС»

Первые ПЛИС можно было сконфигурировать, просто задав положение всех электронных ключей вручную. (Сомнительно, что так делали даже тогда, но теоретически это было возможно). Сейчас же разработка конфигурационной прошивки для ПЛИС, настраивающей ее на выполнение требуемой заказчику функциональности - процесс сложный и многоэтапный. Начинается он, как правило, с описания функциональности устройства на языке высокого уровня. Чаще всего это Verilog либо VHDL, но в последнее время это может быть и C/C++, а так же результаты работы таких программ, как Matlab/Simulink либо LabView.

Слово «программирование» взято в кавычки, т.к. под ним понимается процесс, приводящий в конечном этапе к некоторой функциональной конфигурации ПЛИС, в отличие от программирования для процессорных систем, где программирование – это задание на некотором языке последовательности выполнения действий. Соответственно, основные языки, используемые для задания функциональности ПЛИС – Verilog/SystemVerilog и VHDL, в строгом смысле не являются языками программирования и их называют «языками проектирования аппаратуры» (HDL – Hardware Design Language).

Языки проектирования аппаратуры

Несмотря на явный сдвиг в сторону высокоуровневого проектирования, полностью потенциал программируемой логики можно раскрыть только на классических языках проектирования аппаратуры. Таковых существует всего два – Verilog/SystemVerilog (разработан 1984/2002 гг.) и VHDL (разработан 1983 г.). Эти языки полностью функционально эквивалентны, но имеют абсолютно различный синтаксис. Общие черты HDL-языков:

- Имеют синтезируемое и несинтезируемое подмножество операторов. Именно синтезируемые операторы, описывающие функциональность реальной аппаратуры отличают HDL-языки от обычных языков программирования. В то время как несинтезируемое подмножество используется для симуляции и тестирования и мало отличается от алгоритмических языков программирования.

- Используются для описания параллельно выполняющихся действий.

Отличия:

Verilog/SysnemVerilog по синтаксису похож на язык C, а синтаксис VHDL основан на языке ADA.

В нижеследующей таблице приведены варианты кода на языках Verilog и VHDL для описания простого логического элемента – счетчика с предварительной загрузкой.

| Описание на Verilog | Описание на VHDL |

module counter (rst, clk, load, data, Q); parameter size = 32; input rst; // These inputs/outputs represent input clk; // connections to the module. input load; input [size-1:0] data; output [size-1:0] Q; reg [size-1:0] count; always @ (posedge clk or posedge rst) if (rst) count <= {size{1'b0}}; else begin if (load) count <= data; else count <= count + 1'b1; end assign Q = count endmodule |

library IEEE; use IEEE.std_logic_1164. all; use IEEE.numeric_std. all-- for the unsigned type

entity COUNTER is generic ( WIDTH : in natural := 32); port ( RST : in std_logic; CLK: in std_logic; LOAD : in std_logic; DATA: in std_logic_vector(WIDTH-1 downto 0); Q: out std_logic_vector(WIDTH-1 downto 0)); end entity COUNTER;

architecture RTL of COUNTER is signal CNT : unsigned(WIDTH-1 downto 0); begin process(RST, CLK) is begin if RST = '1' then CNT <= (others => '0'); elsif rising_edge(CLK) then if LOAD = '1' then CNT <= unsigned(DATA); -- type is converted to unsigned else CNT <= CNT + 1; end if; end if; end process;

Q <= std_logic_vector(CNT); -- type is converted back to std_logic_vector end architecture RTL; |

Видно, что описание на Verilog значительно компактнее кода на VHDL, поэтому сейчас язык Verilog используется чаще, чем VHDL. Среди недостатков «чистого» Verilog, часто отмечают отсутствие объектно-ориентированного подхода (при том, что VHDL изначально разрабатывался как объектно-ориентированный язык), но появление языка SystemVerilog полностью устранило этот недостаток. САПР Vivado изначально поддерживает как Verilog/SystemVerilog, так и VHDL, причем в проекте эти языки можно применять одновременно.

Проектирование на языках HDL является стандартным классическим подходом к проектированию, но этот подход отнюдь не единственный. Сейчас получает широкое распространение и популярность т.н. «высокоуровневое проектирование», т.е. разработка аппаратной части системы на высокоуровневых языках программирования, прежде всего – на языках C/C++. Ниже будут рассмотрены несколько широко применяемых при проектировании ПЛИС и СнК маршрутов проектирования.

Экологическая система ПЛИС и СнК

Чтобы эффективно использовать ПЛИС, кроме самой микросхемы, требуется много дополнительных средств, составляющих экосистему разработки и применения ПЛИС.

Прежде всего, к экосистеме ПЛИС относятся программные средства разработки, но также в нее входят jtag-кабели для прошивки и отладки ПЛИС (иногда их называют «программаторами»), отладочные платы и средства, документация и демодизайны, различные форумы разработчиков, производство коммерческих и свободных IP-ядер и многое другое. Так же с 1988 года и по сей день Xilinx издает бесплатный виртуальный XCell Journal, доступный для скачивания в виде pdf-файла.

Средства разработки

Средства разработки для ПЛИС и СнК являются неотъемлемой частью инфраструктуры ПЛИС и в этой области Xilinx удерживает лидерство, постоянно развивая и улучшая свои программные продукты.

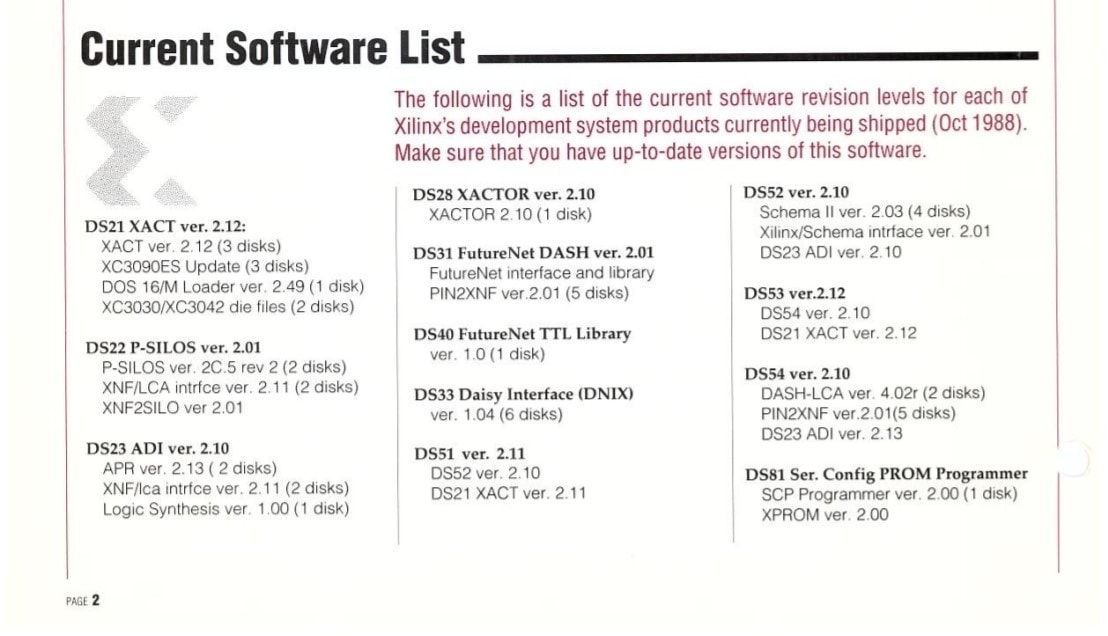

Первые релизы средств разработки Xilinx уже мало кто помнит, но в первом выпуске Xcell Journal они упомянуты – это XACT и XACTOR:

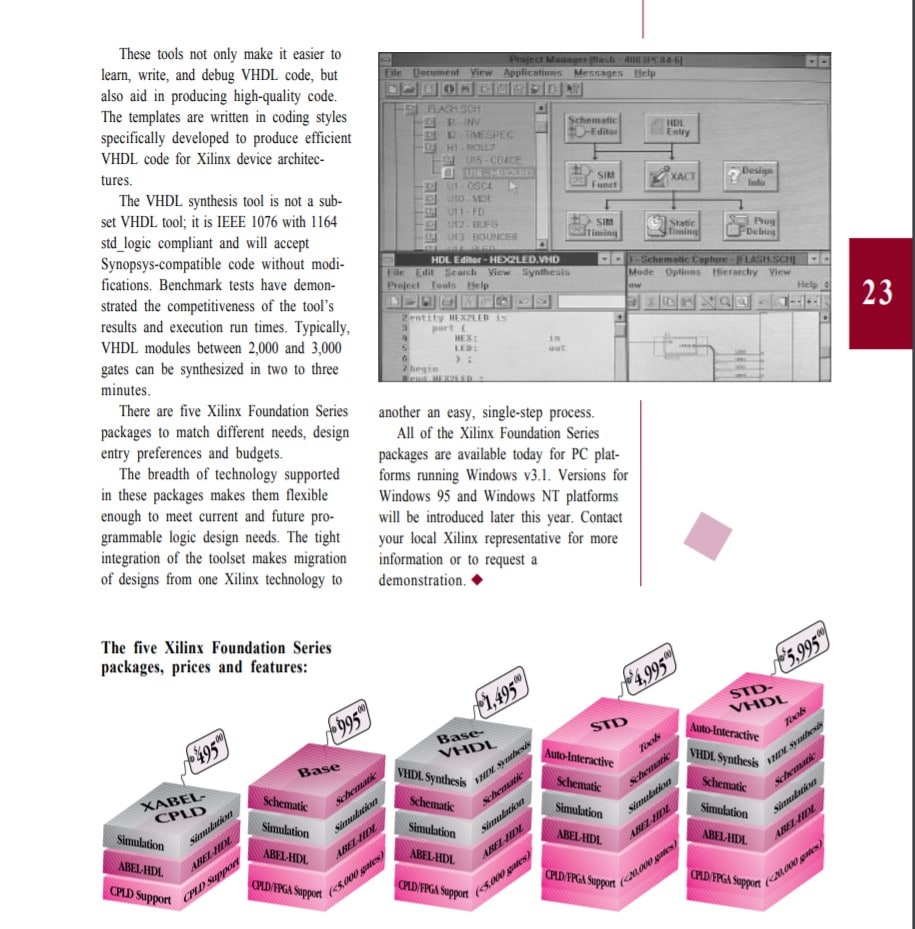

Далее, в 1996 году был создан САПР Foundation, в котором можно было вести разработку как в графическом редакторе, так и на языке VHDL. Ниже приведен анонс из Xcell Journal #21, а те читатели, которые считают цены на ПО высокими, могут ознакомиться с тогдашним прайс-листом.

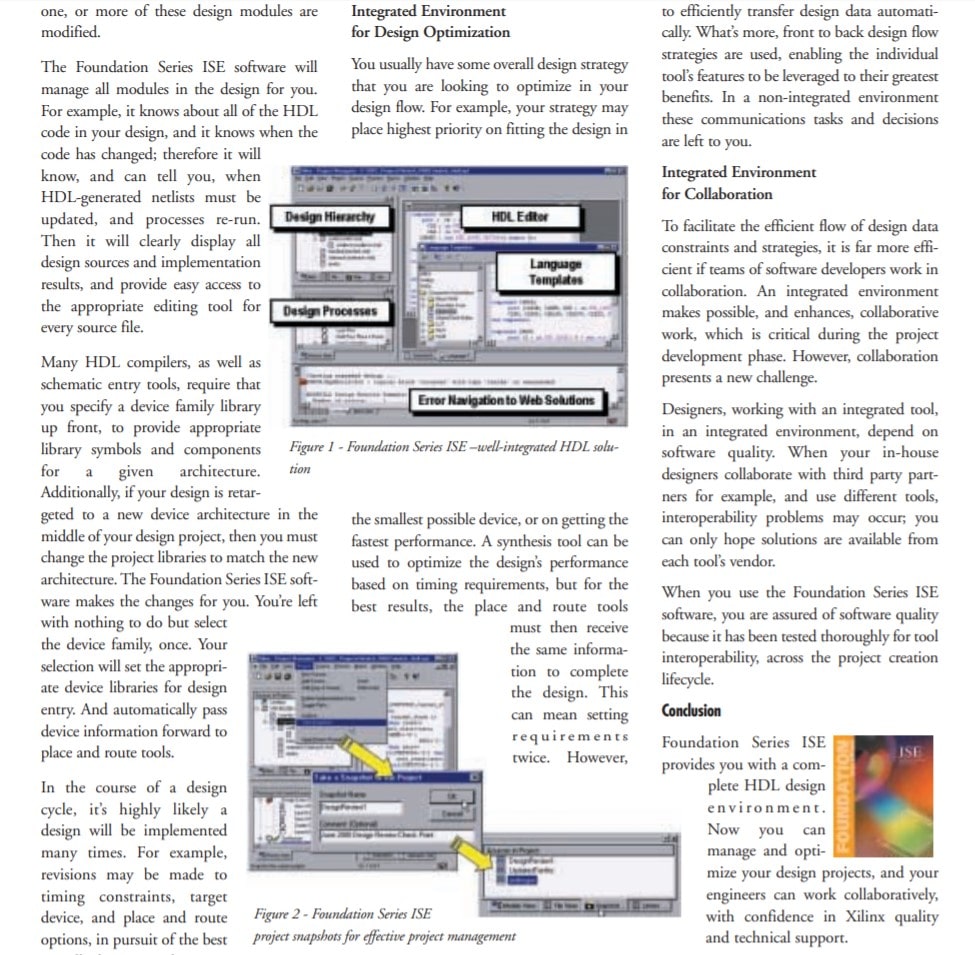

Среда разработки ISE появилась в конце 2000 г. под названием «Xilinx Foundation Series ISE Software». Ниже приведена страничка из Xcell Journal #38 об этом событии:

САПР ISE получился очень удачным и, в том числе, даже по личному опыту, могу сказать, что разработчики его любили. Завершающей версией ISE стал релиз 14.7 от октября 2013 года, когда разработка была прекращена, а проект был заморожен. Однако микросхемы, для которых требуется ISE, все еще серийно выпускаются, поэтому ISE используется даже сейчас. Возможно (но это неточно), что это рекорд продолжительности жизни для САПР!

Следующим САПР от Xilinx стал пакет Vivado, выпущенный в 2014 г., интерфейс которого был создан на базе оболочки PlanAhead из ISE. Данный САПР завершил свою активную фазу в 2019 г., когда был выпущен релиз под номером 2019.1.

Далее, с версии 2019.2, представленной в ноябре 2019 г., Xilinx перешел на САПР Vitis, а Vivado вошел в него составной частью.

Таким образом, на данный момент мы имеем уже пятое поколение средств разработки от Xilinx.

Маршруты проектирования ПЛИС

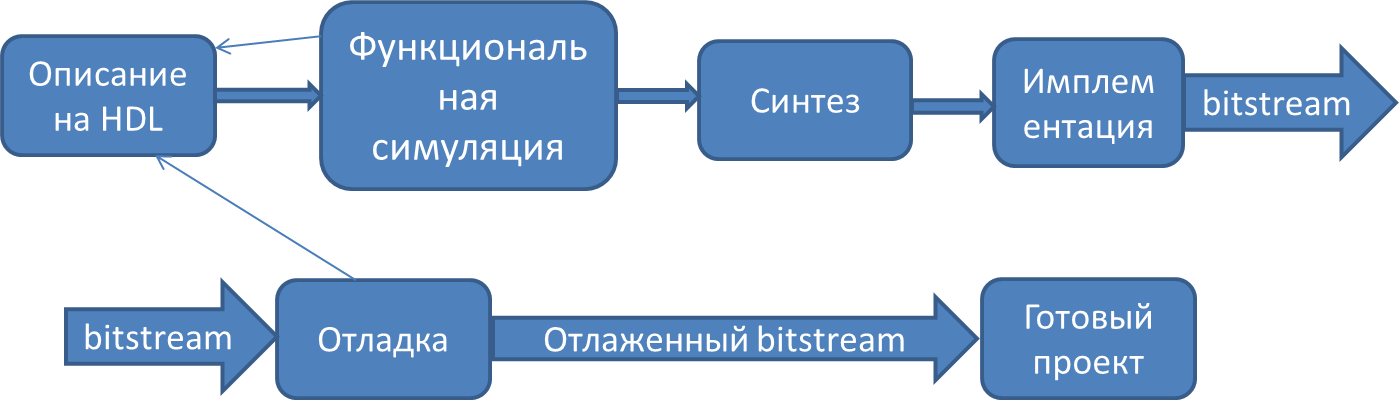

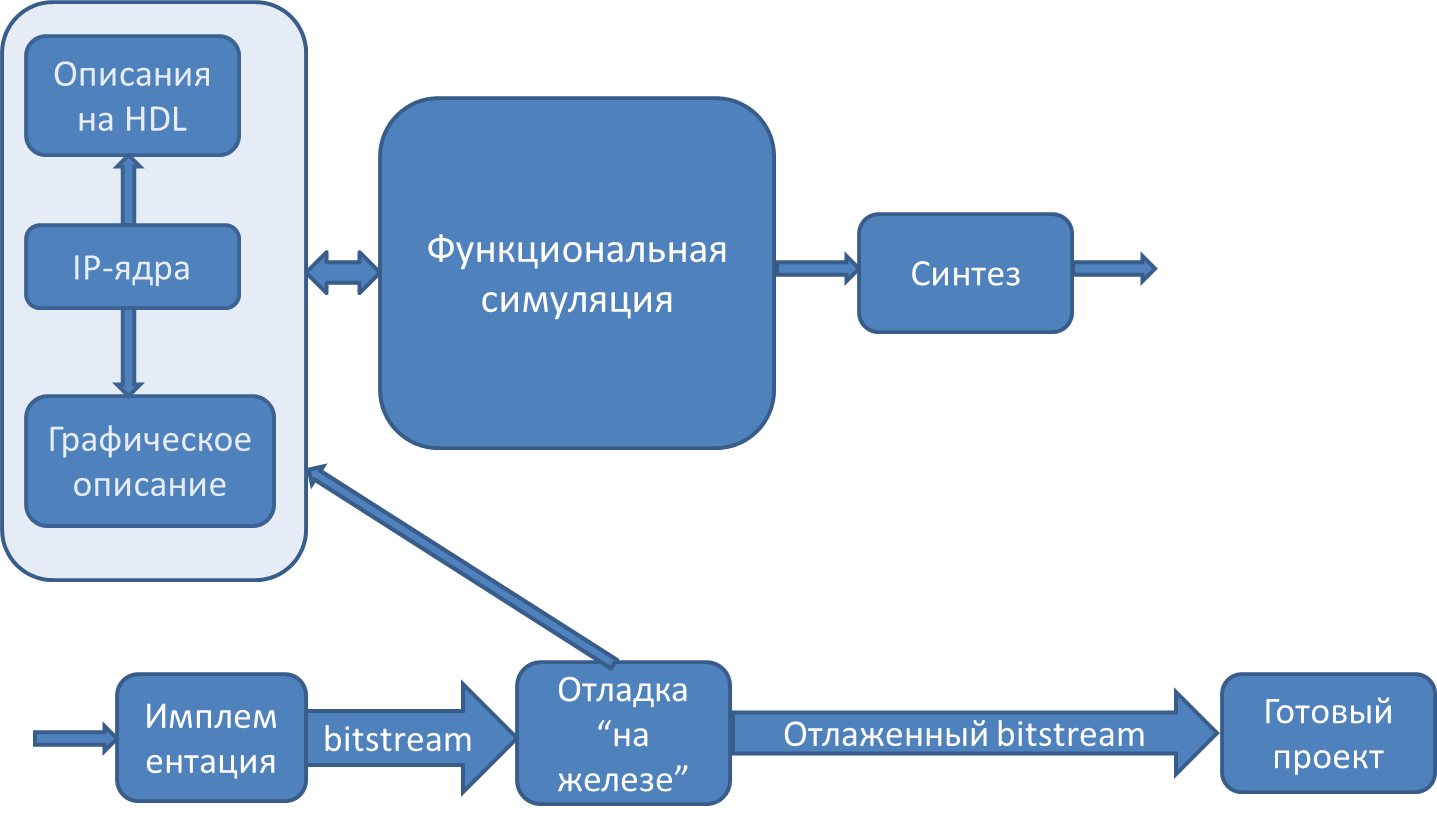

Классический маршрут

Если по данному маршруту проектируется система на кристалле, содержащая процессорную часть, то на выходе мы имеем готовую вычислительную систему, программирование для которой осуществляется стандартными программными средствами.

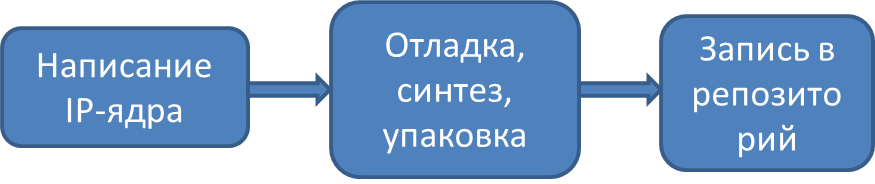

Расширением данного маршрута является проектирование с применением IP-ядер. IP-ядро можно сравнить с API в программировании. Это ранее разработанная и отлаженная часть проекта, выполняющая определенную функциональность. IP-ядра можно хранить отдельно в специальных репозиториях и включать в свои проекты по мере необходимости. Данный маршрут можно считать основным в САПР Vivado:

Соответственно, маршрут проектирования с использованием IP-ядер немного меняется:

Именно этот маршрут проектирования реализован в среде проектирования Vivado.

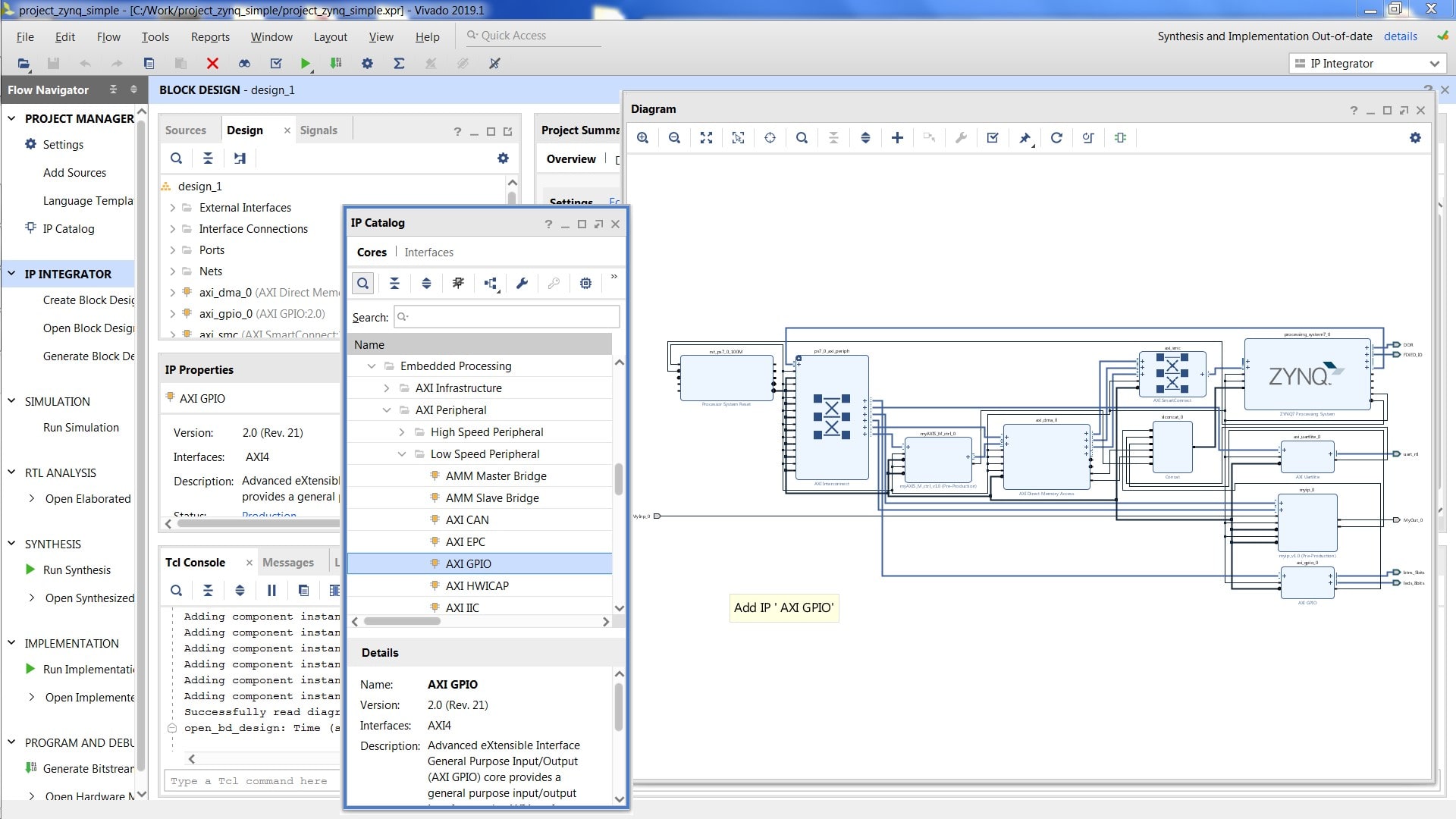

Визуальное проектирование с использованием IP-репозитория

Этот способ проектирования наиболее распространен для проектирования систем на кристалле (т.е. систем с процессорными ядрами), но может применяться и для обычных ПЛИС. В Vivado этот способ широко применяется, причем можно создавать иерархические графические диаграммы и заполнять их из репозиториев различными компонентами. Собственные модули на языках Verilog и VHDL также можно вставлять в эти диаграммы.

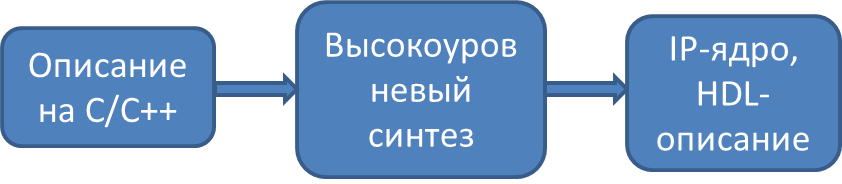

Высокоуровневое проектирование

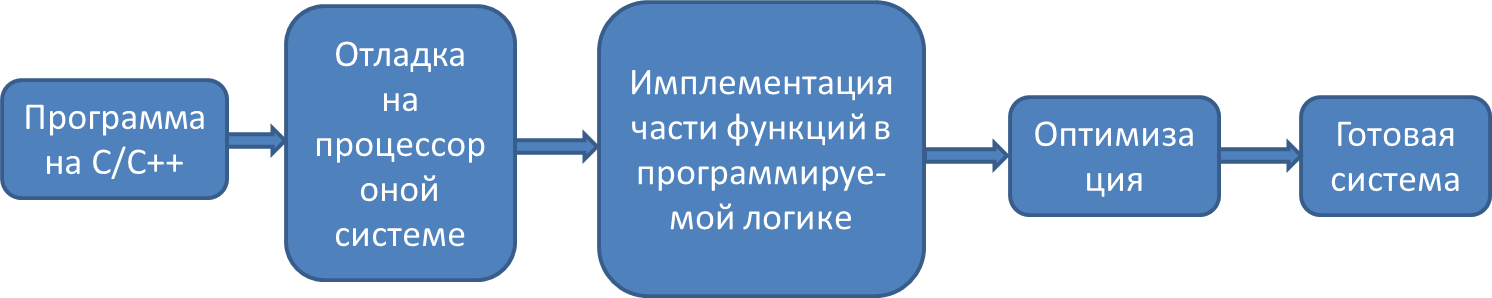

Следующий маршрут проектирования – так называемое «высокоуровневое проектирование», ниже показана диаграмма для этого маршрута. Здесь алгоритм, описываемый на C/C++, реализуется в программируемой логике в виде IP-ядра. Затем это IP-ядро может быть включено в любой проект. А весь проект имплементирован по классическому маршруту.

Имеется еще один высокоуровневый маршрут проектирования, применяемый для систем на кристалле. Данный маршрут проектирования является стандартным в новейшем САПР Vitis.

Этот маршрут проектирования начинается с написания программы на C/C++. Затем производится профилирование программного кода и определение функций, замедляющих работу системы. С целью повышения скорости работы этих функций они реализуются в программируемой логике и, при необходимости, подвергаются дальнейшей оптимизации.

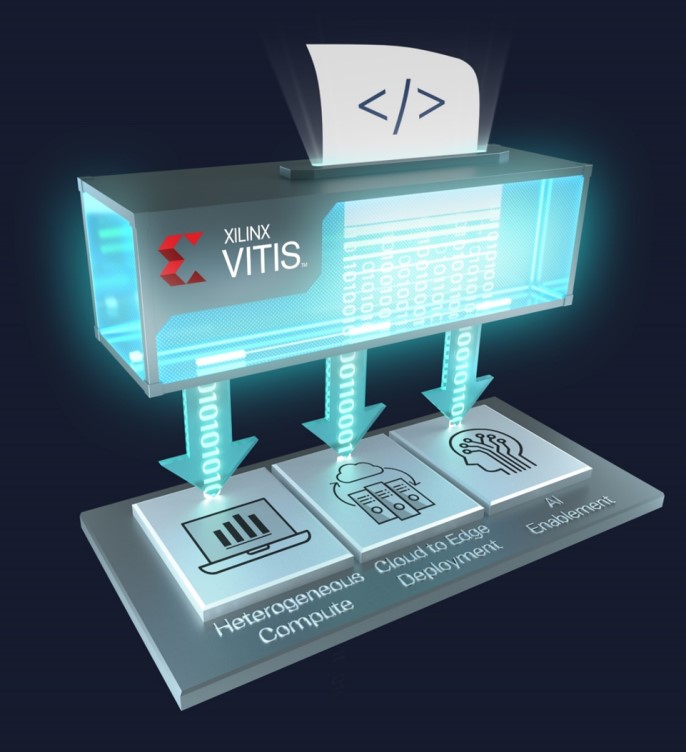

Новейшая среда разработки Vitis (на рис выше) предназначена для проектирования на самых современных системах на кристалле Xilinx, включая выводимое на рынок семейство Versal, а также для ускорительных платформ Alveo.

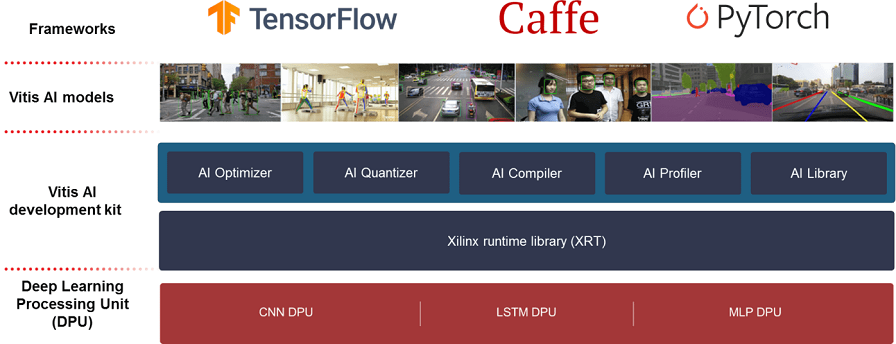

Среда разработки Vitis™ AI - это платформа разработки Xilinx для вывода ИИ на аппаратных платформах Xilinx

Vitis позволяет решать самые сложные задачи в различных предметных областях, включая разработку систем искусственного интеллекта. Это достигается путем интеграции Vitis со специализированными пакетами. Например, для разработки систем искусственного интеллекта на базе ПЛИС и СнК Xilinx, используется пакет VitisAI, структура которого показана ниже.

Анализируя маршруты проектирования, можно сделать вывод, что проектирование для программируемой логики движется в сторону сближения с классическим программированием. Это позволяет расширить применение программируемой логики за счет привлечения программистов, которым не нужно разбираться в тонкостях архитектуры ПЛИС.

Отметим также, что классические маршруты проектирования реализуют методику «снизу-вверх», т.е. сначала разрабатывалась аппаратная часть, производилась ее верификация сначала на уровне блоков и модулей, а затем полностью собранная система. Затем для этой системы можно было разрабатывать программное обеспечение. В то же время методология высокоуровневого проектирования наиболее эффективна при реализации метода «сверху вниз», т.е разработка начинается с создания и отладки программного обеспечения, а аппаратная часть конфигурируется уже под требования разработанного программного продукта.

Выводы:

Компании на данный момент удалось создать наиболее совершенные и мощные средства проектирования в отрасли. Однако для полного раскрытия потенциала этих средств требуется их квалифицированное применение, а для этого, в свою очередь, компаниям необходимо регулярно повышать квалификацию своих ведущих разработчиков.

Вебинар: Начало работы с Xilinx Vivado HLS

Автор: Викулин Владимир, инженер по применению Xilinx компании Макро Групп.

Любые вопросы по продукции Xilinx задавайте по телефону 8 (800) 333-06-05

Ссылки:

- Сайт Xilinx, url: https://www.xilinx.com/

- Электронный журнал «XCell Journal»

- Википедия, статья «ПЛИС», url: https://ru.wikipedia.org/wiki/ПЛИС

- Википедия, статья «Язык описания аппаратуры», url: https://ru.wikipedia.org/wiki/язык_описания_аппаратуры

- Википедия, статья «Логический синтез», url: https://ru.wikipedia.org/wiki/Логический_синтез

Обновление Март 2021 года.

Обучение проектированию и программированию ПЛИС в системе Vivado

Компания МакроГрупп совместно с компанией PLC2 – европейским лидером в обучении технологиям проектирования на ПЛИС и СнК, открывает программу обучения российских специалистов по программам и при участии PLC2. Выдается сертификат от компаний МакроГрупп и PLC2.

На данный момент доступны учебные курсы, посвященные маршруту проектирования Vivado:

- Введение в проектирование в системе Vivado

- Проектный маршрут проектирования в Vivado

- Применение TCL в Vivado (Несколько курсов)

- Непроектный маршрут в Vivado

- Маршрут ECO в Vivado

В дальнейшем номенклатура учебных курсов будет существенно расширена.

Обучение доступно в виде онлайн-вебинаров, очных тренингов, также возможно проведение корпоративных тренингов. Приглашаем компании и заинтересованных в дополнительном профессиональном обучении специалистов принять участие в тренингах в удобном для Вас формате.