Xilinx выводит на рынок серию ПЛИС SPARTAN-7

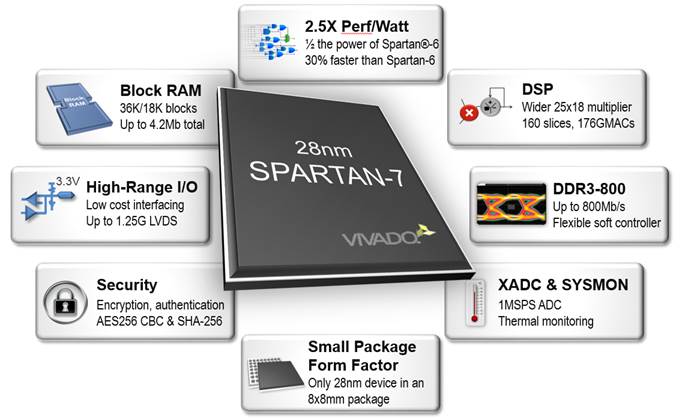

Компания Xilinx анонсировала новую бюджетную серию ПЛИС Spartan-7. Новая серия ПЛИС выполнена по технологическим нормам 28 нм и ориентирована применение в устройствах нижнего ценового сегмента. Серия Spartan-7 на 30% быстрее предшественницы серии Spartan-6, имеет наилучшие среди ПЛИС соотношения производительности к потребляемой мощности и соотношение стоимости к количеству вводов-выводов.

Серия FPGA Spartan-7 состоит из шести устройств, характеристики которых перечислены в нижеследующей таблице:

|

ПЛИС Spartan®-7 Наименьшая цена за один вывод и наивысшее соотношение производительность/потребляемая мощность |

||||||

|---|---|---|---|---|---|---|

| Номер для заказа | XC7S6 | XC7S15 | XC7S25 | XC7S50 | XC7S75 | XC7S100 |

| Количество логических ячеек | 6 000 | 12 800 | 23 360 | 52 160 | 76 800 | 102 400 |

| Количество слайсов | 938 | 2 000 | 3 650 | 8 151 | 12 000 | 16 000 |

| Количество триггеров | 7 500 | 16 000 | 29 200 | 65 200 | 96 000 | 128 000 |

| Объем распределенной памяти (Кб) | 70 | 150 | 313 | 600 | 832 | 1,100 |

| Блочная память | ||||||

| Колич. блоков по 36 Кб | 5 | 10 | 45 | 75 | 90 | 120 |

| Общий объем (Кб) | 180 | 360 | 1 620 | 2 700 | 3 240 | 4 320 |

| Блоки управления частотой (1 MMCM + 1 PLL) | 2 | 2 | 3 | 5 | 8 | 8 |

| Макс. число В/В | 100 | 100 | 150 | 250 | 400 | 400 |

| Из них, диф. пар | 48 | 48 | 72 | 120 | 192 | 192 |

| Блоки DSP | 10 | 20 | 80 | 120 | 140 | 160 |

| Блок AMS/XADC | 0 | 0 | 1 | 1 | 1 | 1 |

| Блоки конфигурирования AES/HMAC | 0 | 0 | 1 | 1 | 1 | 1 |

| Скорость (Коммерч. исп.) | -1,-2 | -1,-2 | -1,-2 | -1,-2 | -1,-2 | -1,-2 |

| Скорость (Индустр. исп.) | -1,-2,-1L | -1,-2,-1L | -1,-2,-1L | -1,-2,-1L | -1,-2,-1L | -1,-2,-1L |

| Корпус | Размер (мм) | Доступные В/В: 3,3 В SelectIO™ HR I/O | |||||

| CPGA196 | 8x8 | 86 | 86 | ||||

| CSGA225 | 13x13 | 100 | 100 | 150 | |||

| CSGA324 | 15x15 | 150 | 210 | ||||

| TQGA144 | 20x20 | 72 | 72 | 60 | |||

| FGGA484 | 23x23 | 250 | 338 | 338 | |||

| FGGA676 | 27x27 | 400 | 400 | ||||

Несколько фактов по новым устройствам ПЛИС SPARTAN-7:

- количество логических элементов от 6 000 до 102 400;

- поддержка памяти DDR3 до 800 Мб/с;

- системный монитор и встроенный АЦП (до 17 входных каналов)

- размер корпуса от 8 мм до 28 мм (шаг 0,5 мм – 1 мм);

- совместимость с IP инфраструктурой седьмого семейства;

- поддержка средами проектирования Vivado Design Suite (включая Vivado HLS) и бесплатной версией WebPack

По планам компании Xilinx инженерные образцы станут доступны в первом квартале 2017 года, а в массовое производство будет развернуто в 2018 году.

По всем вопросам, связанным с приобретением, поддержкой и получением раннего доступа к образцам обращайтесь к официальному поставщику Xilinx в России компании «Макро Групп», пишите нам через форму «Задать вопрос» или позвоните по телефону 8 (800) 333-06-05.