Xilinx демонстрирует технологию 56 Гбит трансиверов

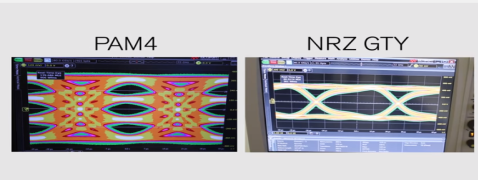

В марте компания Xilinx объявила о разработке 56 Гбит приемопередатчиков на основе 16 нм FinFET технологии FPGA с использованием амплитудно-импульсной модуляции 4-уровня АИМ4 (PAM4 – Pulse mplitude Modulation). Признанные в отрасли наиболее масштабируемыми, решения PAM4 помогут зародить следующую волну развертывания Ethernet сетей путем удвоения пропускной способности на существующей инфраструктуре. Xilinx демонстрирует инновационную технологию 56 Гбит одним из первых. Она предназначена для 400 Гбит и 1 Тбит интерфейсов высокой плотности оборудования передачи данных следующего поколения и означает выход на новый уровень развития Ethernet технологий.

Такие технологии как Cloud Computing, Industrial IoT и сети с программноопределяемыми параметрами (Software-Defined Networks) должны масштабироваться до 50 Гбит, 100 Гбит, 400 Гбит, а также терабитных интерфейсов, чтобы максимизировать плотность портов без увеличения стоимости на бит. Стандартизованные показатели линий следующего поколения имеют решающее значение для удовлетворения растущих требований к пропускной способности. Xilinx прилагает усилия в стандартизации технологии 56 Гбит PAM4 в рамках межсетевого оптического форума (МОФ) и совместно с Институтом инженеров электротехники и электроники (IEEE). Технология PAM4 56 Гбит трансивера компании Xilinx была разработана совместно с TSMC с целью преодоления физических ограничений традиционной передачи данных по таким характеристикам линии как: вносимые потери и перекрестные помехи.

Посмотрите демонстрацию компанией Xilinx 56 Гбит PAM4 трансиверов в рамках выставки OFC (г. Анахайм, США) 22 - 24 марта. http://www.xilinx.com/video/technology/56g-pam4-transceiver.html