Устройства Versal на платформе ACAP от Xilinx

2 октября 2018 года на Форуме Разработчиков Xilinx (XDF) компания анонсировала новую революционную платформу ACAP (Адаптивная Платформа Ускорения Вычислений, на этапе разработки – Everest Project), а так же семейство кристаллов, изготовленных на новой платформе под названием Versal. Устройства изготавливаются на тайваньской фабрике TSMC по технологическим нормам 7 нм.

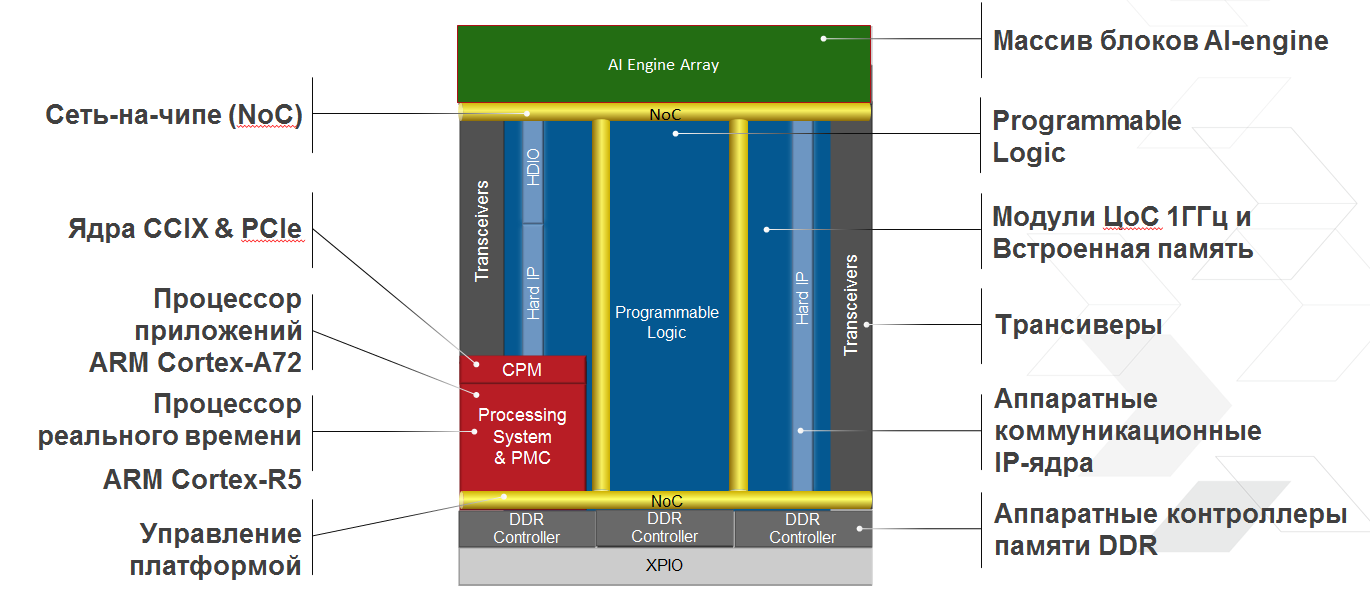

Платформа ACAP представляет собой разработанный Xilinx новый класс устройств, содержащий, наряду с уже применяемыми блоками (гетерогенные ARM-ядра, матрица программируемой логики), революционные новые узлы: высокопроизводительная внутричиповая сеть, ускорители AI Engine (используются для векторных вычислений, в том числе – при реализации нейросетей) и интегрированная оболочка для взаимодействия с внешним окружением.

Впервые примененная внутричиповая сеть обеспечивает суммарную полосу более 1 Тб/с, что более чем достаточно для межблочной коммуникации. В то же время, многие традиционные блоки были значительно модернизированы. Например, блоки DSP наконец-то «научились» производить операции с плавающей точкой.

Платформа ACAP, имея, по сравнению с Zynq MPSoC, в несколько раз большую производительность, предназначена для решения широкого круга задач, в том числе для создания систем искусственного интеллекта реального времени на базе нейронных сетей. В семействе имеется две серии: для применения в системах искусственного интеллекта – AI (см. рис. ниже) и универсальная Prime (без массива AI).

Серия AI состоит из 5 устройств, а Prime – из 9.

Характеристики, номенклатура и состав серий уже определены:

| Ресурсы и характеристики семейства ACAP | Серия AI | Серия Prime |

|---|---|---|

| Внутричиповая сеть | Да | Да |

| Суммарная производительность операций с данными INT8( Топ/с) | 49-147 | 3-27 |

| Колич. Логич. Ячеек (Тыс.) | 540-1968 | 352-2154 |

| Встроенная память (Мб) | 68-191 | 40-324 |

| Блоки DSP с поддержкой операций с плавающей точкой | 928-1968 | 472-3984 |

| Блоки AI | 128-400 | нет |

| Процессорная система (APU) | Dual-core Arm Cortex-A72; 48KB/32KB L1 Cache w/ parity and ECC; 1MB L2 Cache w/ ECC | |

| Процессорная система (RPU) | Dual-core Arm Cortex-R5; 32KB/32KB L1 Cache, and TCM w/ECC | |

| Последовательные трансиверы (NRZ, PAM4) | 8–44 | 12–66 |

| Макс. Производительность трансивееров (Тб/с) | 2,9 | 4,2 |

| Колич. Вводов-выводов | 346–692 | 238–778 |

| Колич. Контроллеров памяти | 2-4 | 1-6 |

Инженерные образцы ACAP Versal будут доступны с 4-го квартала 2019 года, а в 2020 году ожидается появление серийных устройств.

За дополнительной информацией обращайтесь в компанию Макро Групп, которая является официальным партнером Xilinx, либо непосредственно на сайт Xilinx по адресу www.xilinx.com/versal

По всем вопросам, связанным с приобретением и поддержкой продукции Xilinx, включая приобретение лицензий, напишите нам через форму «Задать вопрос» или позвоните по телефону 8 (800) 333-06-05.