Среда разработки Vivado 2019.2 от Xilinx доступна для скачивания

Компания Xilinx выпустила релиз средств разработки Vivado 2019.2, который содержит в себе новые возможности

Поддержка новых устройств:

- Kintex UltraScale: XQRKU060 в аэрокосмическом исполнении;

- Кинтекс-7: XA7K160T;

- Virtex UltraScale+ HBM: XCVU31P, XCVU33P, XCVU35P, XCVU37P.

Среда разработки Vivado:

- добавлена поддержка веб-установщика на основе командной строки, что повышает удобство работы и производительность при установке инструментов Xilinx;

- произведена оптимизация использования диска для уменьшения размера установленного ПО;

- прекращён выпуск DVD-дисков с дистрибутивом Vivado.

Системный генератор для DSP:

- поддерживаемые версии MATLAB: R2018a, R2018b и R2019;

- в библиотеку блоков добавлены два новых блока суперсэмплирования.

Vivado-HLS:

- функции C могут быть помечены как чёрные ящики и заменены эквивалентными модулями RTL, предоставленными пользователем;

- массивы данных теперь могут считываться несколькими потребителями, для чего введена новая прагма;

- для улучшения параллельного выполнения, последовательность буферов для пинг-понга потока данных может быть указана через отдельную прагму/директиву;

- модифицированная прагма/директива для памяти позволяет указать тип хранилища и время ожидания;

- пользователь может установить прагму/директиву ap_ctrl_none для потока данных для повышения пропускной способности.

Библиотеки C:

- добавлен шаблон для функции FFT на языке C ++ с супер-частотой дискретизацией (SSR). Реализована систолическая архитектура, поддерживающая несколько выборок данных (целочисленная или фиксированная) в каждом такте;

- введена расширенная поддержка OpenCV через xfOpenCV (см. документацию);

- полный набор функций math.h теперь оптимизирован для типов данных с фиксированной запятой.

RTL-синтез:

- добавлены функции VHDL-2008, включая параметры (generics) в пакетах, параметризуемые функции в описании функциональных модулей функции, задаваемые в параметрах;

- инкрементальный синтез теперь доступен с дополнительным автоинкрементным режимом для проектов Vivado.

Средство Model Composer:

- в библиотеке блоков DSP теперь доступны новые блоки: FFT, IFFT и FIR для разработки и реализации алгоритмов обработки сигналов

- для увеличения пропускной способности расширен список поддерживаемых блоков

- дополнительные блоки, поддерживающие потоковую передачу данных позволяют разрабатывать и внедрять алгоритмы с высокими требованиями к пропускной способности, используя расширенный набор блоков, поддерживающих операции с потоковой передачей данных. Примеры: справочная таблица, задержка, умножение матрицы, подматрица и т. д.

- расширенная комплексная поддержка в C/C ++ импорта функций: добавлена поддержка импорта функций, которые также используют типы hls::x_complex, в дополнение к std::complex, расширена поддержка сложных сигналов в пользовательских блоках

- усовершенствования в импорте функций C/C ++: создание пользовательских блоков «Source» для вашего проекта с использованием функции xmcImportFunction

- улучшенная поддержка сигналов Row-Matrix и Column-Matrix: улучшения инфраструктуры генерации кода для обработки сигналов Row-Matrix [Nx1] и Column-Matrix [1xN] в проекте, что приводит к повышению производительности;

- поддерживаемые версии MATLAB: R2018a, R2018b и R2019a.

Улучшения в IDE:

- автоматически добавлять новые прогоны (runs) в сводные панели проекта;

- введена опция «Сохранить как» для стратегий отчетов.

Отладочные платы и примеры проектов:

- введена функция загрузки и установки сторонних плат прямо с Github одним кликом в графическом интерфейсе.

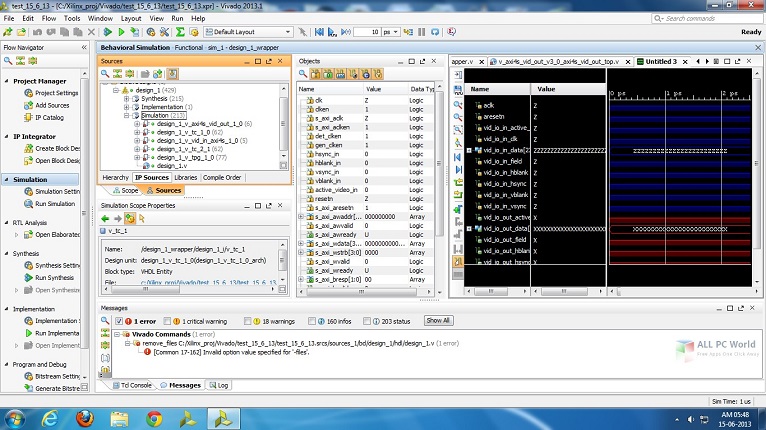

Vivado Simulator:

- в SystemVerilog добавлена поддержка расчёта функционального покрытия и генерации отчётов (.txt или .html);

- поддержка ассертов о свойстве и последовательности в параллельной области. Расширенная поддержка рандомизации ограничений (constraints). Новое окно экземпляра протокола для отображения интерфейсов AXI в дизайне;

- функция «Mark Simulation» на блок-схеме для непосредственного добавления интерфейсов AXI в средство просмотра сигналов.

IP блоки:

- зашифрованные блоки в проекте будут скрыты в средстве просмотра схемы и иерархии. Введено новое правило «xilinx_schematic_visibility», которое можно включать /выключать, чтобы изменить поведение по умолчанию;

- обновлён открытый ключ Xilinx Vivado, как часть регулярного обновления безопасности.

Имплементация:

- новые AXI Regslice IP для пересечения регионов супер-логики на высокой скорости и автоматической вставки конвейеров;

- увеличена тактовая частота для Virtex UltraScale + HBM (до 450 МГц);

- механизм на основе свойств доступен для пользовательских шин и интерфейсов для всех устройств UltraScale и UltraScale+;

- ускоренная физическая оптимизация сетей с большим фанаутом;

- автоматическое использование регионов пересечения супер-логики позволяет повысить производительность и улучшить качество разводки;

- отчёт по методологии отчётов работает в 2 раза быстрее для проектов с большим количеством временных констрейнтов;

- opt_design добавляет опцию переназначения SRL для преобразования между примитивами регистра сдвига SRL и цепочками регистров. Позволяет сбалансировать использование и производительность.

Анализ проекта и констрейнты:

- Pblocks: границы Pblock могут быть сделаны подвижными, чтобы позволить им перемещаться по мере необходимости для повышения производительности.

Документация о начале работы в Vivado 2019:

Скачать Vivado Design Suite User Guide Programming and Debugging UG908 (v2019.2) October 30, 2019

Компания Макро Групп является официальным партнером Xilinx.

По всем вопросам, связанным с приобретением и поддержкой продукции Xilinx, включая приобретение лицензий, напишите нам через форму «Задать вопрос» или позвоните по телефону 8 (800) 333-06-05.

Вебинар: Начало работы с Xilinx Vivado HLS