Серверные процессоры LS3C6000 компании Loongson

Компания Loongson Technology начала производство серии серверных процессоров LS3C6000, призванных заменить предыдущее поколение LS3С5000.

Loongson Technology является значимым игроком в полупроводниковой отрасли Китая, с фокусом на разработку собственных процессоров и технологий. Производитель Loongson занимает значимую часть китайского рынка, сотрудничает со многими компании внутри «Поднебесной». Особым вниманием хотелось бы выделить их линейку серверного направления – серию LS3Cxxxx. Предыдущее поколение, LS3С5000, постепенно замещается современным, последним в линейке, чипом LC3С6000.

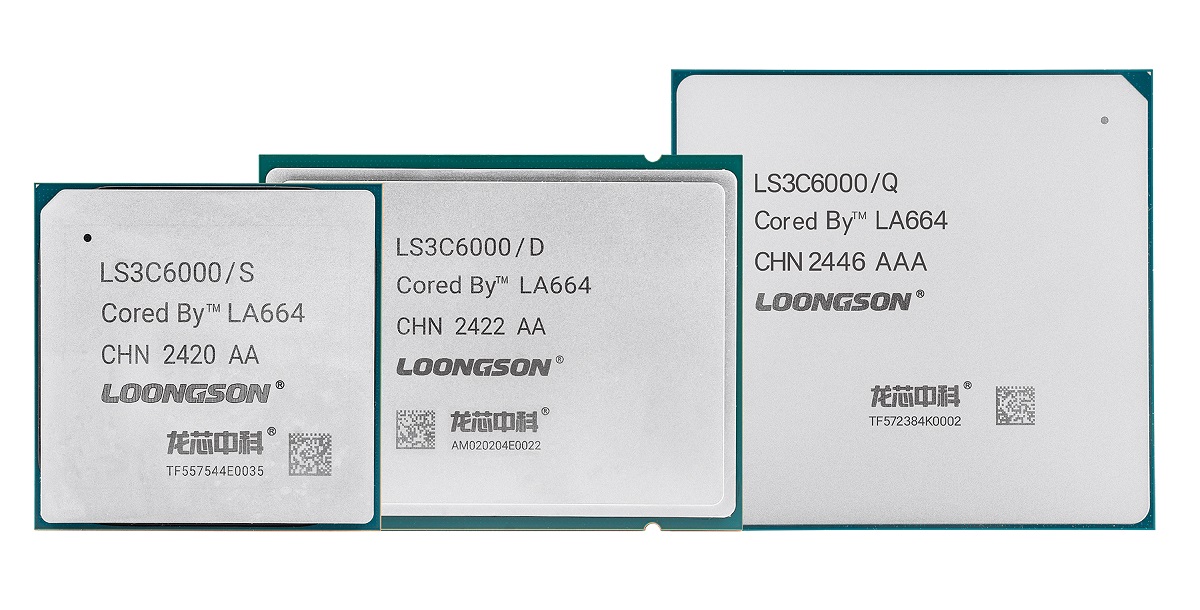

Процессоры серии Loongson LS3C6000 построены на базе микропроцессорной архитектуры Loongson 4-го поколения, объединяющей 16 ядер LA664 на одном кристалле с поддержкой 32 логических ядер благодаря технологии одновременной многопоточности. Серия LS3C6000, основанная на технологии Loongson Coherent Link, поддерживает три конфигурации корпусов с различным количеством кристаллов (S/D/Q). Благодаря многоканальным прямым соединениям на уровне платы процессоры могут масштабироваться до 256 логических ядер, обеспечивая значительную вычислительную мощность для различных сценариев применения. Это эффективно удовлетворяет потребности пользователей как в высокопроизводительных одноядерных процессорах, так и в многоядерных процессорах с высоким уровнем параллелизма.

В зависимости от конфигурации, в процессор интегрировано 16 (LS3С6000S), 32 (LS3С6000D) или 64 физических ядра (LS3С6000Q).

Основные характеристики процессоров серии LC3C6000 представлены в таблице ниже:

|

Частота |

2…2,2 ГГц |

|

Пиковая скорость вычислений с плавающей точкой двойной точности |

844,8 Гфлопс @ 2,2 ГГц (S) 1612,8 Гфлопс @ 2,1 ГГц (D) 3072 Гфлопс @ 2,0 ГГц (Q) |

|

Физические ядра |

16(S) / 32(D) / 64(Q) |

|

Логические ядра |

32(S) / 64(D) / 128(Q) |

|

Описание ядра |

64-битные суперскалярные ядра LA664. Поддержка LoongArch™ ISA. 128/256-битные векторные инструкции и шестиэтапное внеочередное выполнение. 4 блока с фиксированной точкой, 4 векторных блока и 4 блока доступа к памяти. |

|

Кэш |

Каждое ядро имеет 64 КБ частного кэша инструкций L1 и 64 КБ частного кэша данных L1. Каждое ядро имеет 256 КБ частного кэша L2. Общий объём кэша L3 составляет 32 МБ. |

|

Память |

4 × 72-битная память DDR4-3200 (S)

8 × 72-битная память DDR4-3200 (D, Q) |

|

Высокоскоростной ввод-вывод |

4(S) / 8(D, Q) интерфейса PCIE 4.0 ×16, мультиплексированные по 8 (S) / 16(D, Q) контроллерам; один интерфейс x16 может быть сконфигурирован как Loongson Coherent Link (LCL) для межчипового взаимодействия |

|

Другие вводы-выводы |

1 SPI, 1 UART, 3 I2C, 1 AVS, 16 × GPIO |

|

Корпус |

FCBGA2422 (S) FCLGA4126 (D) FCBGA6128 (Q) |

|

Особенности управления питанием |

динамическое отключение тактовых генераторов основного модуля; динамическое масштабирование частоты основных тактовых доменов; динамическое регулирование напряжения основных доменов |

|

Энергопотребление |

100…120 Вт @ 2,2 ГГц (S) 180…200 Вт @ 2,1 ГГц (D) 250…300 Вт @ 2,0 ГГц (Q) |

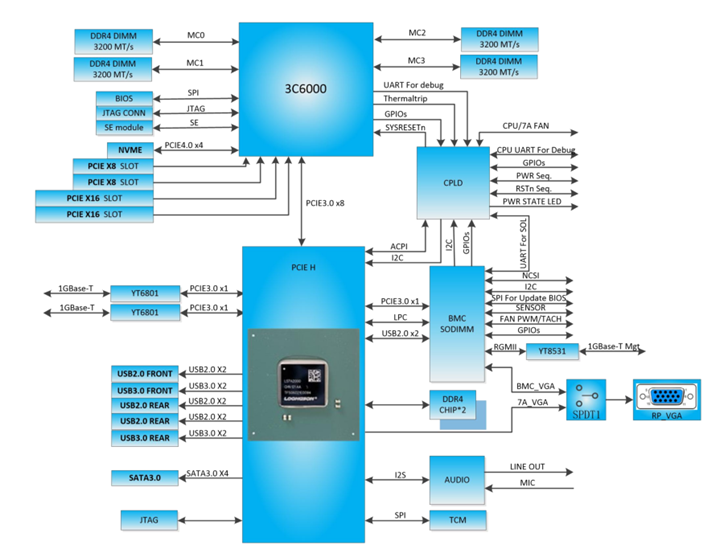

К процессору LS3С6000 предоставляется весь инструментарий разработчика, включая отладочную плату. Функциональная схема представлена на изображении ниже:

Пример платы с одним сокетом представлен на изображении ниже: