Ускорение бимформинга (процесса формирования луча) на платформе Xilinx Vitis

Аннотация

Это исследование было проведено с целью демонстрации преимуществ ускорения расчетных операций бимформинга с использованием унифицированной программной платформы Xilinx® Vitis™ для ускорения расчетов при формировании диаграммы направленности (beamforming). Технология Vitis обеспечивает реализацию параллельного выполнения такого числа задач, которое соответствует требованиям к производительности для конкретно взятой системы. В данном исследовании также продемонстрирована необходимость управления потоком данных в интерфейсе, который использует ускорительный модуль. Изменение формы двухмерных массивов будет иметь важное значение для оптимизации потоков данных, поступающих в модуль и исходящих из него.

Исходные коды и файлы (скачать)

Цели и задачи

В результате проведения этого исследования вы научитесь:

- Создавать проекты Vitis с использованием интерфейса пользователя.

- Использовать режим Software Emulation для проверки корректности примера Beamformer с точки зрения функциональности.

- Управлять процессом высокоуровневого проектирования (HLS) с помощью прагмам/директив для проведения сравнительного анализа вариантов реализации касательно параллелизма и потока данных интерфейса.

- Использовать режим Hardware Emulation для определения производительности ядра и ресурсов, определенных в процессе высокоуровневого проектирования.

Вступление

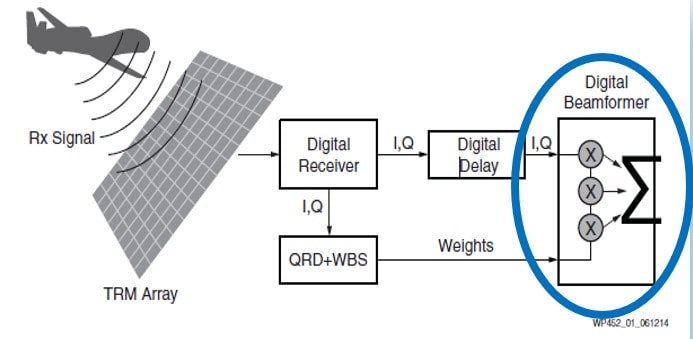

В ходе лабораторной работы будет реализован алгоритм вычисления цифрового формирователя диаграммы направленности (обведено на рисунке ниже).

Сложные данные, генерируемые датчиками приемника фазированной решетки (RX_I и RX_Q), поступают в модуль бимформинга в виде двумерного массива: [SAMPLES] [CHANNELS]. Подобным образом данные об адаптивных весовых коэффициентах сохраняются в виде двумерного массива [BEAMS] [CHANNELS]. Данные о выходном луче (beams_i и beams_q) вычисляются для каждой выборки [BEAMS] [Sample].

![Данные о выходном луче (beams_i и beams_q) вычисляются для каждой выборки [BEAMS] [Sample].](/upload/articles/2020/04-003/1569871136551-min.jpg)

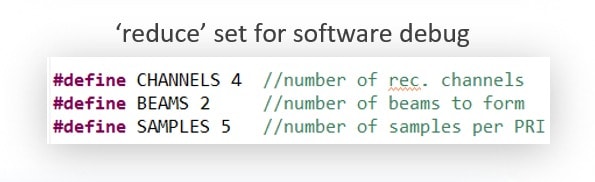

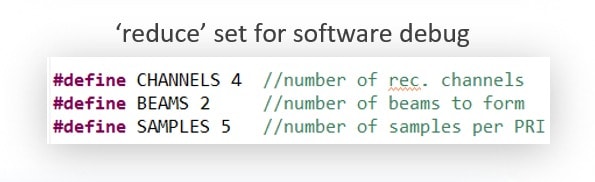

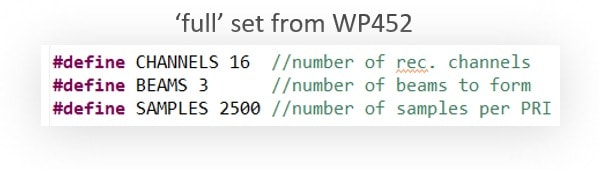

В данном примере бимформинга используются два набора параметров для CHANNELS, BEAMS и SAMPLES – «сокращенный» и «полный». «Сокращенный» набор параметров (представлен на Рисунках 1-3) позволяет упростить отладку программы при сохранении потока данных архитектуры.

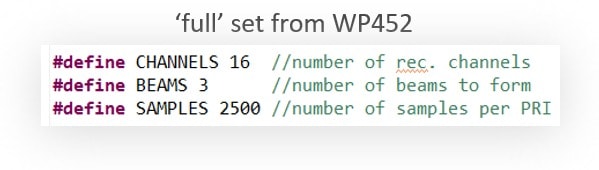

Рисунок, представленный ниже, демонстрирует «полный» набор параметров, используемый в примере Радара (документ WP452).

Номера примеров соответствуют значению интервала повторения импульсов (PRI). Этот интервал (PRI) определяет требования к скорости реализации процесса формирования луча (бимформинга). В данном примере необходимо добиться PRI < 200 мкс. Чтобы получить дополнительные сведения смотрите документ WP452.

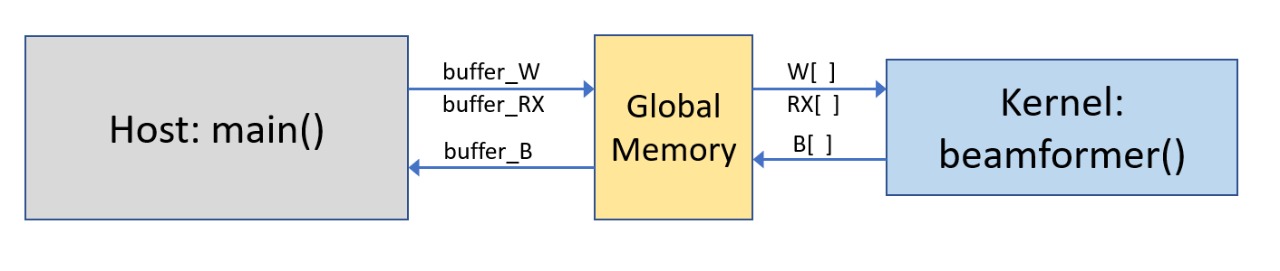

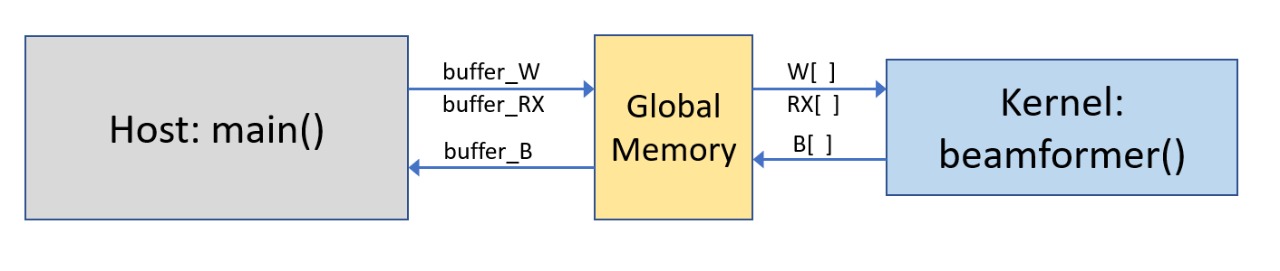

Общая структура приложения представлена на этой блок-схеме, включая все вычисления бимформера, выполненные с использованием кода на C++ в Kernel (метод «beamformer()»).

Код на C++ в Host генерирует данные RX (с датчика) и W (весовые коэффициенты), а затем выполняет самопроверку данных B (бимформинга), возвращающихся из Kernel. Код Kernel будет смоделирован в программной эмуляции (Шаг 3) и использован для работы в плате Xilinx Alveo U200 на этапе аппаратной эмуляции (Шаг 5).

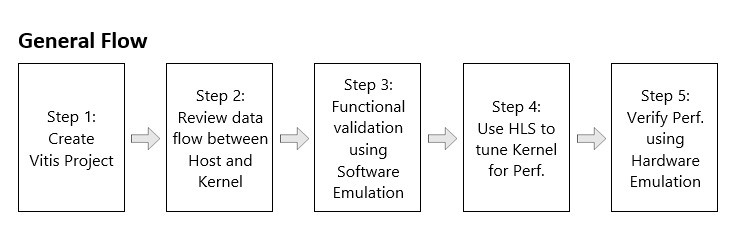

Шаг 1 - Создание проекта Vitis

1.1. Используйте Prompt системы Linux чтобы открыть программу Vitis

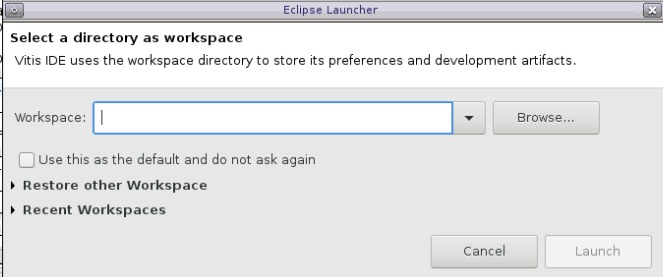

1.2. Выберите рабочее пространство и запустите

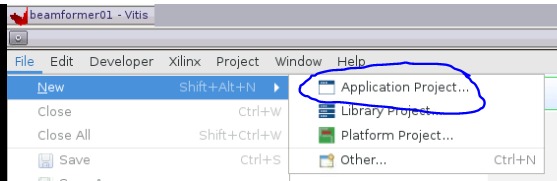

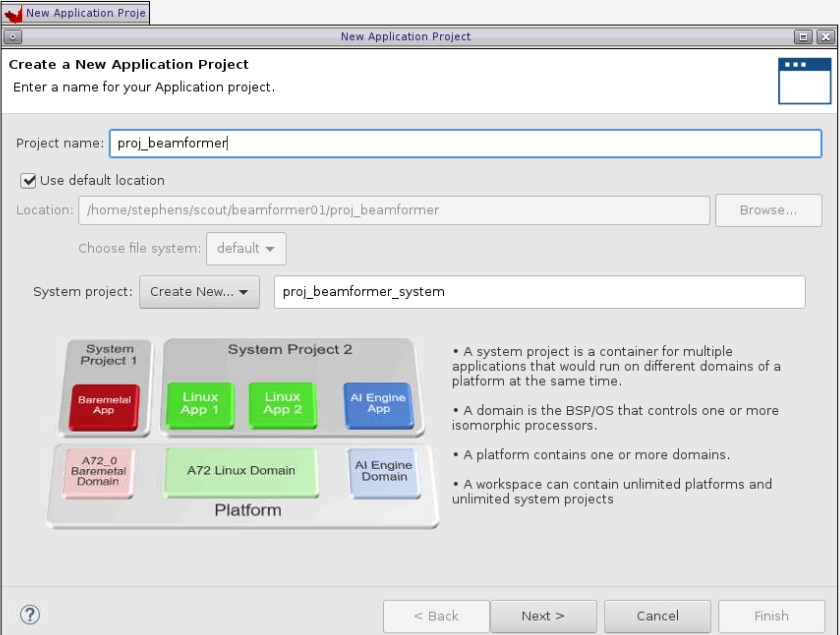

1.3. Создайте новый проект (Application Project)

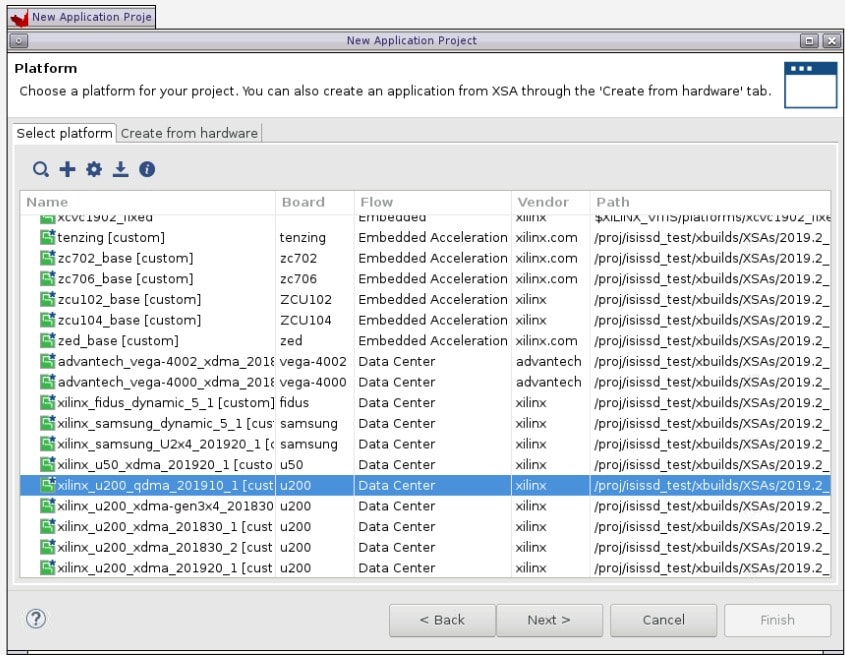

1.4. Дайте имя проекту и выберите платформу

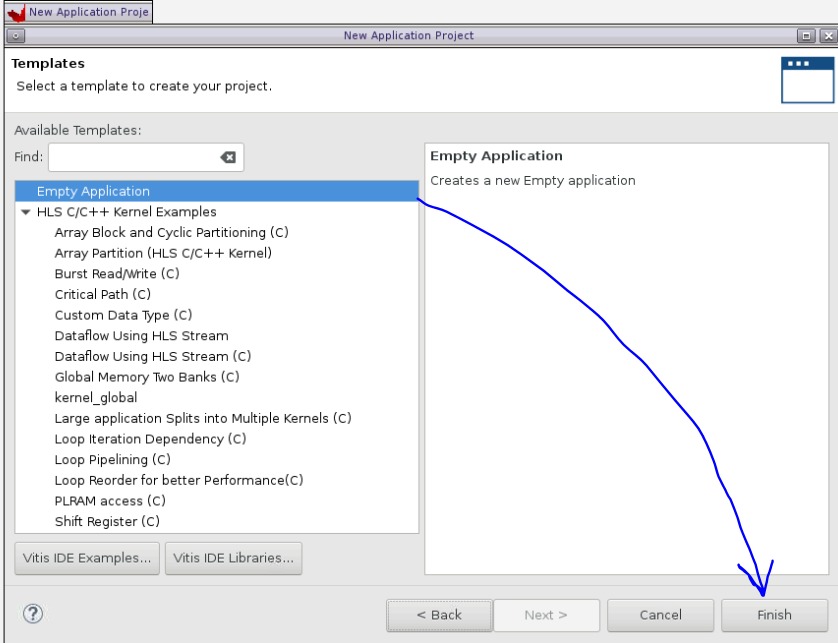

1.5. Выберите пустой проект (Empty Project) и подтвердите.

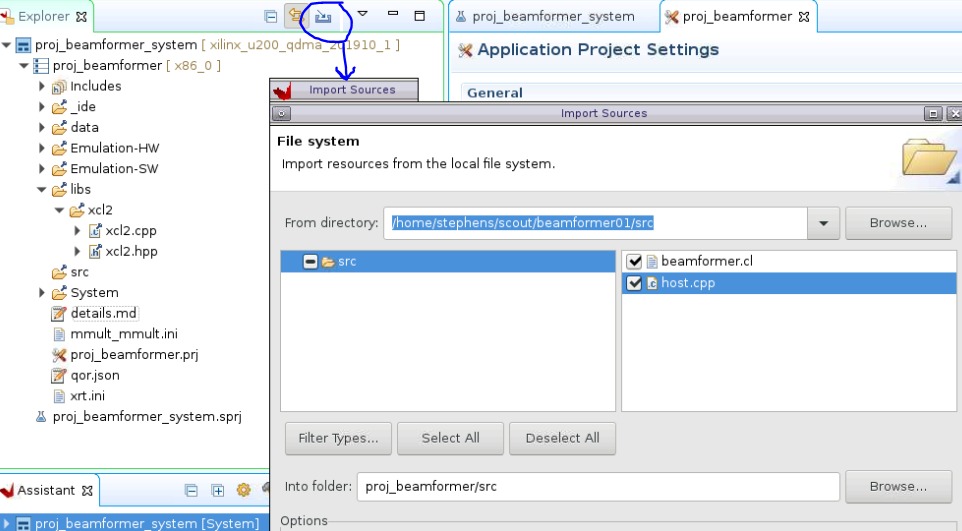

1.6. Импортируйте программные коды Host (host.cpp) и Kernel (beamformer.cl) в проект

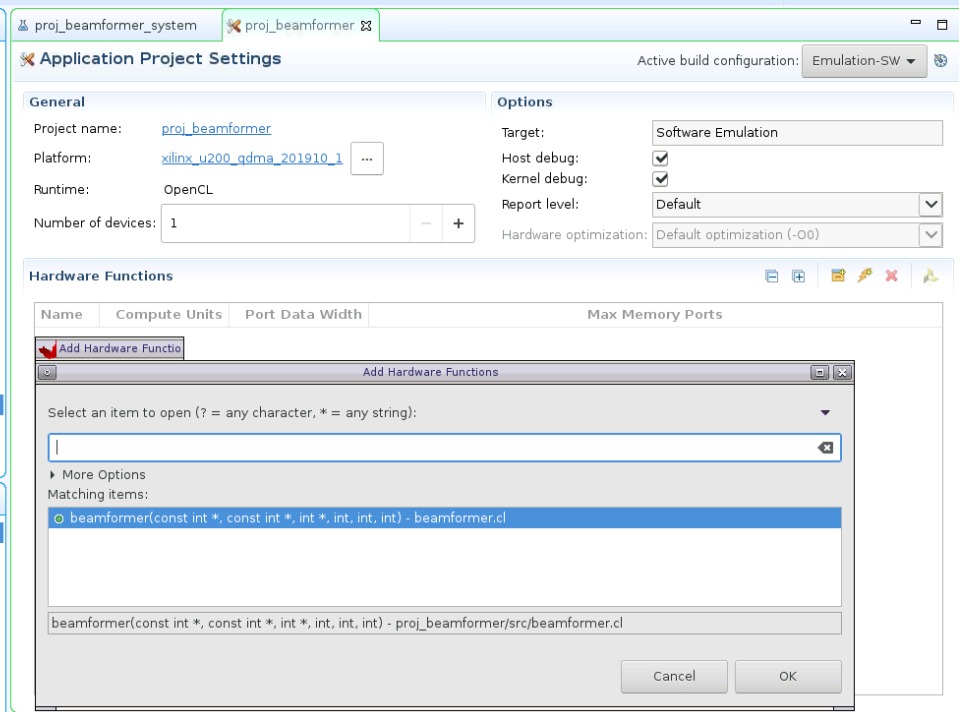

1.7. В разделе с настройками проекта выберите пункт «Add Hardware Function» и подтвердите

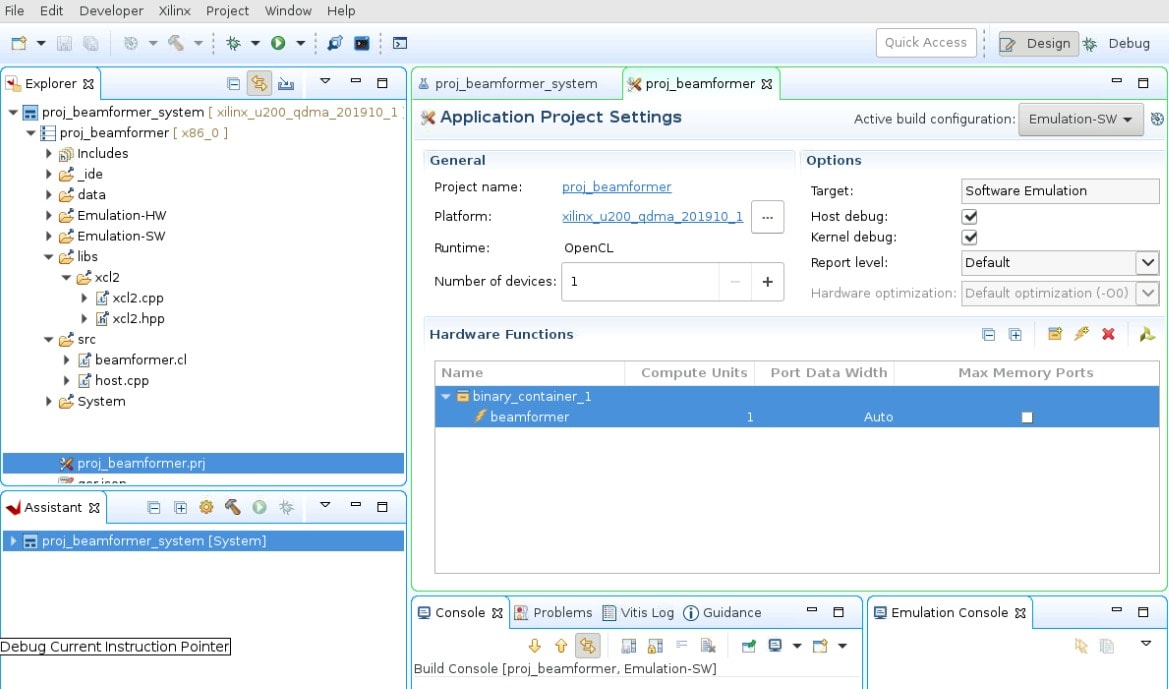

1.8. Корректно конфигурированный проект должен выглядеть так, как показано на рисунке ниже.

Шаг 2 – Исследование потока данных между Host и Kernel

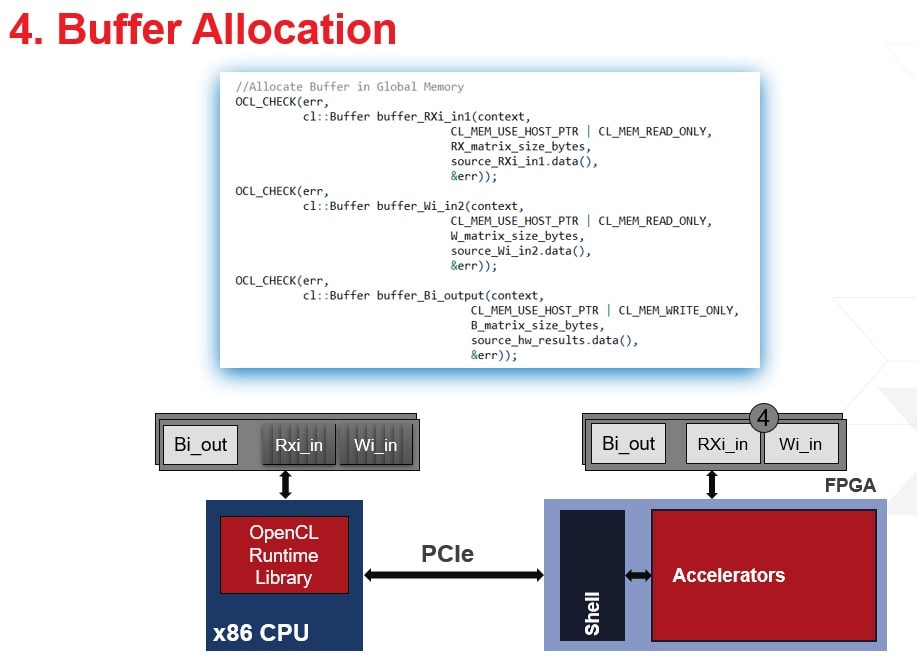

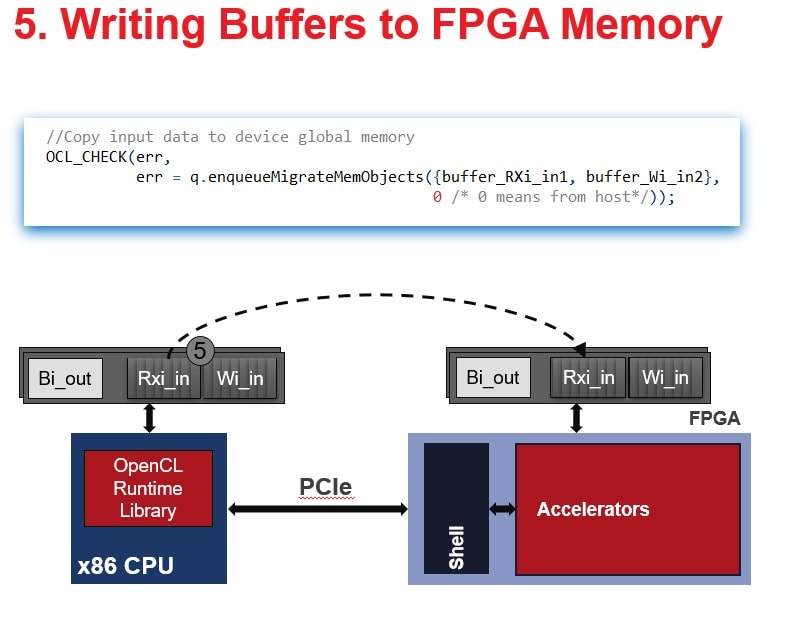

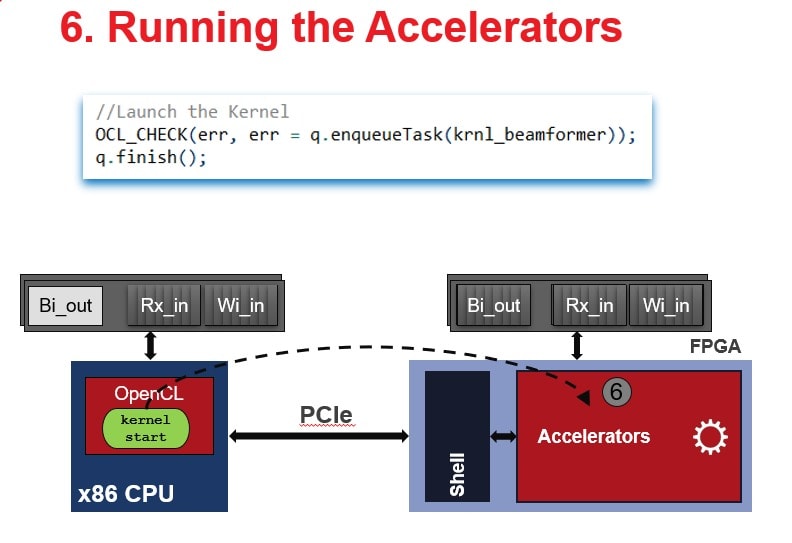

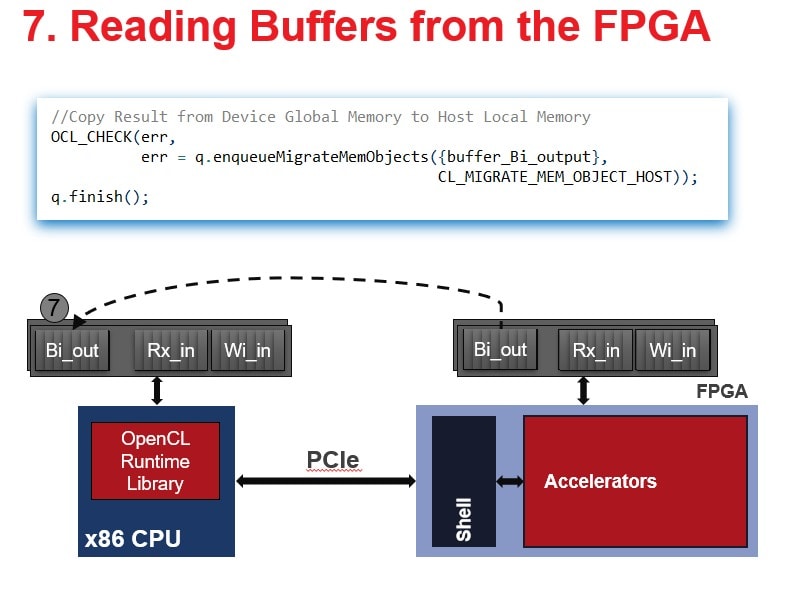

В этом разделе будет использована схема потока данных между Host и Kernel. Представленная здесь модель выполнения содержит этапы перемещения данных (шаги 4-7), для которых выделены команды API в коде HOST.

2.1. Выделите буферы в Global Memory

2.2. Запишите данные RX и Weights (весовых коэффициентов) в Global Memory

2.3. Запустите ускоритель Kernel

2.4. Скопируйте результаты из глобальной памяти в локальную память хоста

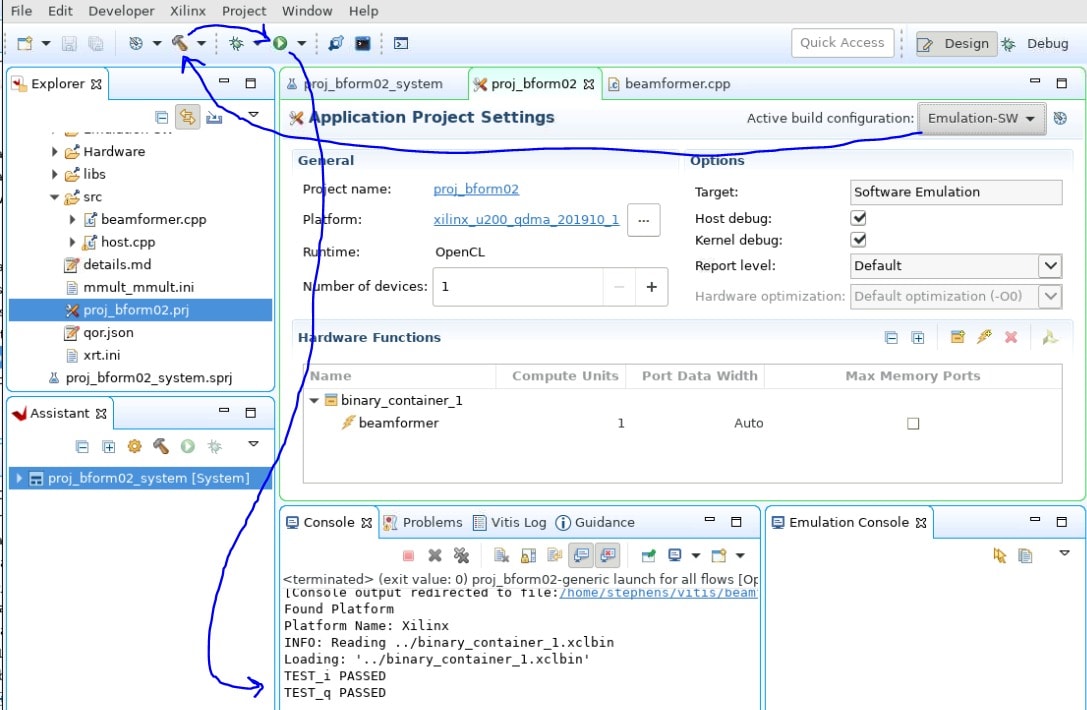

Шаг 3 – Программная эмуляция проекта на протформе Vitis

В этом разделе будут показаны шаги, используемые для функциональной проверки кода Host и Kernel с применением потока программной эмуляции Vitis.

Обратите внимание на то, что код Host генерирует стимулы Weight (buffer_W) и Receiver (buffer_RX) и выполняет проверку корректности возвращаемых данных Beam (buffer_B).

3.1. В режиме просмотра проекта Vitis выберите конфигурацию сборки «Emulation-SW» и нажмите «Build».

3.2. По нажатию на «Run» будет запущена эмуляция Emulation-SW для проверки работоспособности.

3.3. При успешном завершении проверки в консоли отобразится следующее:

3.4 Если в результате изменения кода эмуляция не выполняется, запустите Debug Perspective и используйте обычные точки останова, одношаговое и переменное отображения для поиска проблемной части кода.

Шаг 4 – Использование HLS для ускорения производительности Kernel

В этом разделе будет использован HLS для настройки производительности ядра бимформинга с применением указателей.

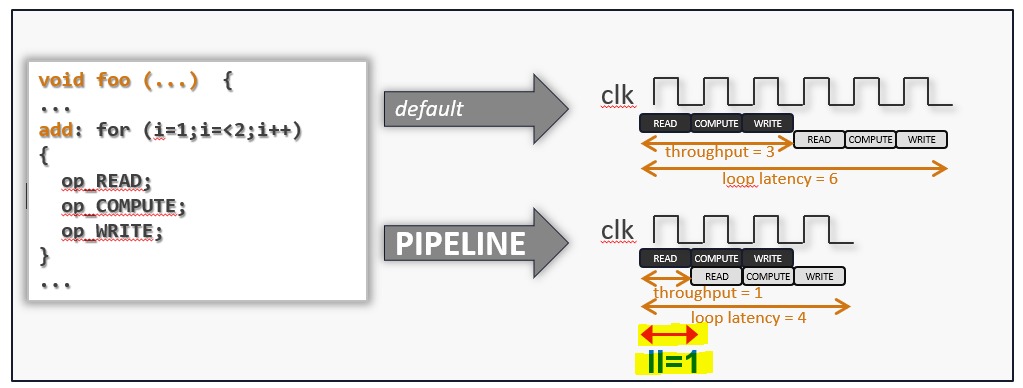

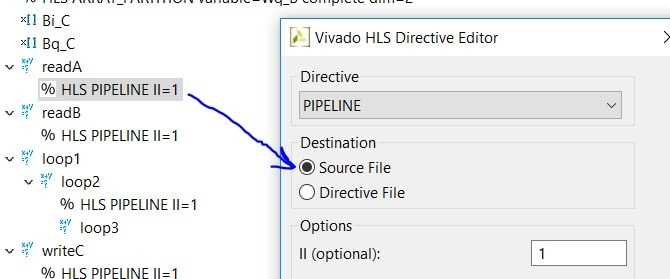

Конвейер PIPELINE дает указание HLS проводить обработку переменных непрерывно, не дожидаясь завершения цикла или выхода из функции. Ниже представлен пример цикла с обработкой по умолчанию (в сравнении с применением PIPELINE).

Как видно, PIPELINE разрешает операцию нового чтения данных на последовательных тактах – это возможно при II=1 (Интервал Инициации). Такая производительность является наилучшей для потока данных, и мы стремимся достичь ее в нашем примере с бимформингом.

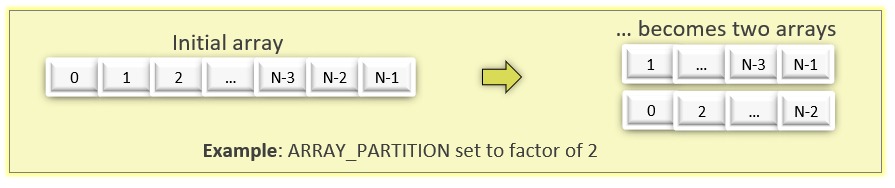

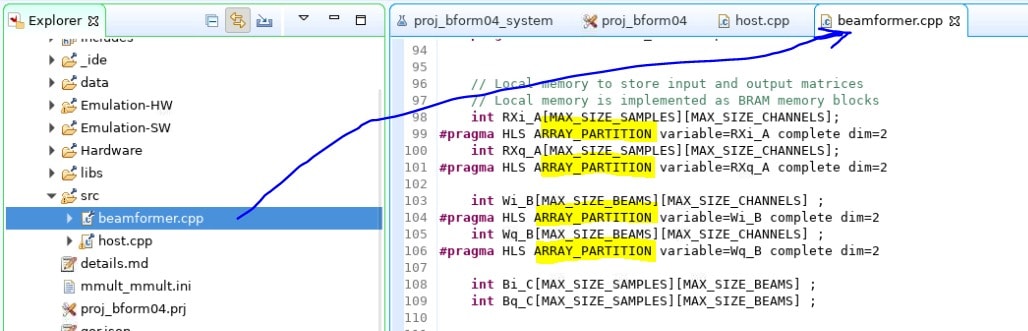

ARRAY_PARTITION способен изменять форму массива для обеспечения более широкого доступа к данным. Он позволяет получать массивы любой формы на основе исходных массивов. Данный метод предназначен для устранения узких мест в памяти чтобы достичь наилучшего значения коэффициента II.

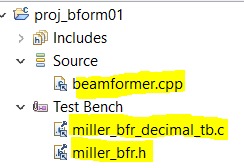

4.1. Создайте проект HLS с файлами Source и Test Bench. Данное исследование упускает некоторые отдельные шаги для потока HLS (подробная информация по основам HLS представлена в документе UG87).

4.2. Первоначально файл ‘beamformer.cpp’ имеет параметры CHANNELS, SAMPLES и BEAMS в рамках "сокращенного" набора. Предоставленный тестовый проект использует эти настройки - пока оставьте их без изменений.

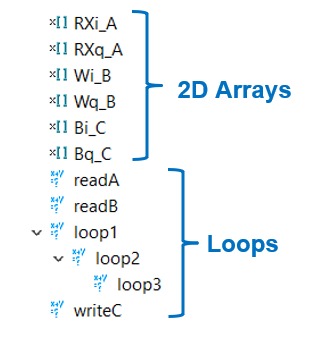

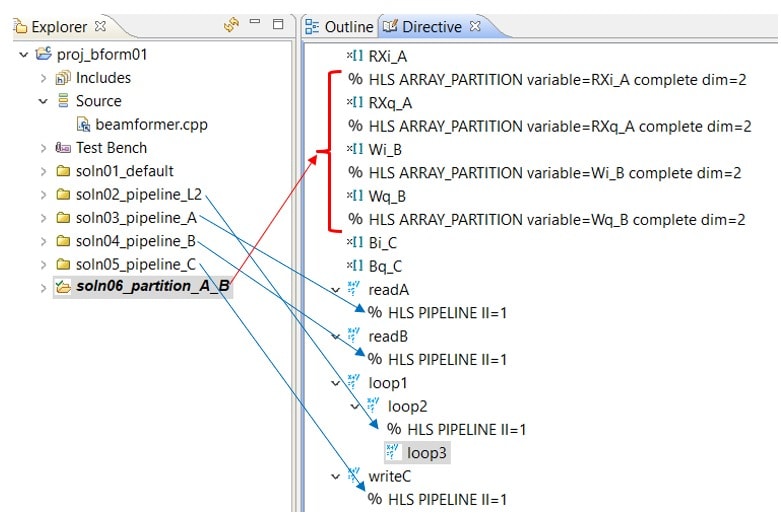

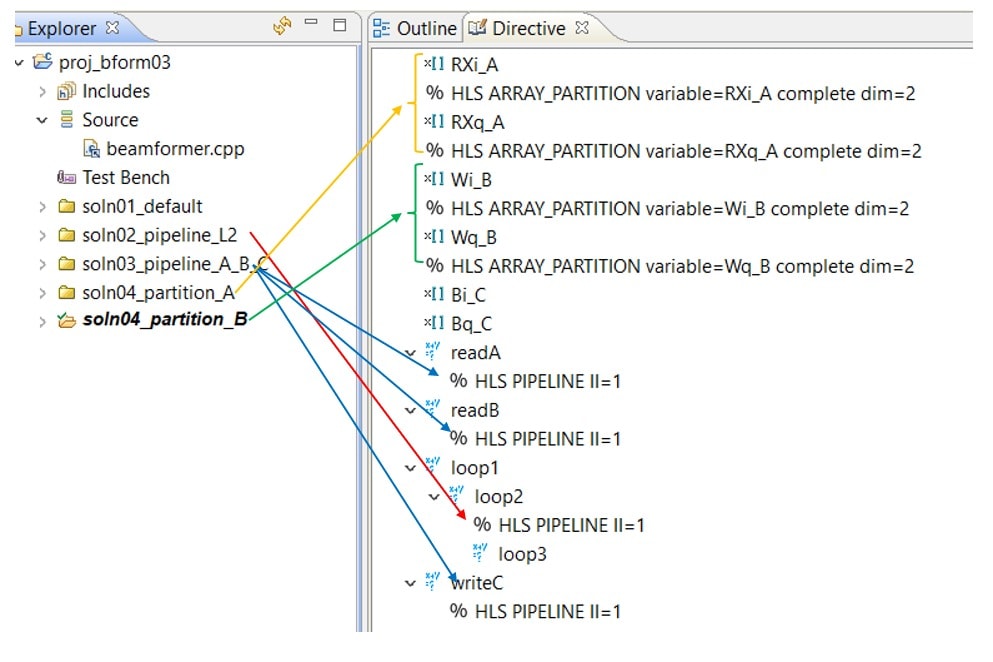

4.3. Поэкспериментируйте с применением указателей PIPELINE и ARRAY_PARTITION к различным циклам и массивам, указанным здесь.

4.4. Рекомендуемая последовательность указателей состоит в том, чтобы вы смогли протестировать все представленные варианты. Они включают в себя указатели, взятые из предыдущего решения.

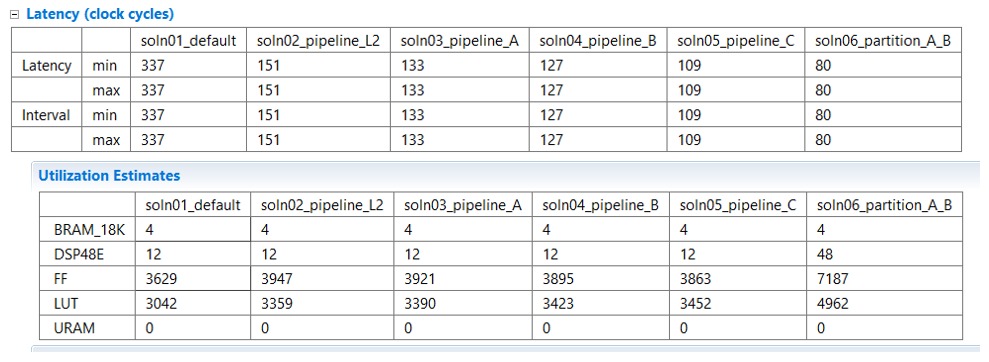

4.5. Ниже представлены данные о задержках (Latency) и ресурсах (Resources) для представленных выше решений 1-6.

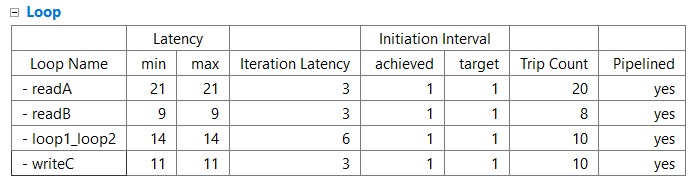

4.6. Soln06_partition_A_B имеет лучшие результаты с задержкой равной 80 тактов (подробные сведения о цикле представлены ниже). Обратите внимание, что для всех циклов был получен II равный 1. Из этого следует, что данные на каждом такте могут быть переданы в любой цикл.

4.7. Выберите «полный» набор параметров.

4.8. Снова используйте указатели PIPELINE и ARRAY_PARTITION для реализации решения с наименьшей задержкой и II=1. На рисунке ниже обозначены все необходимые действия. Во все решения включены указатели из предыдущего решения.

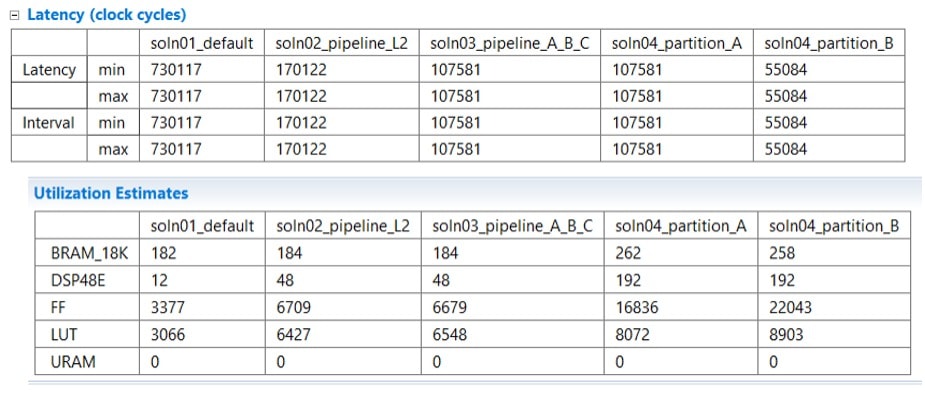

Различия в полученных данных для различных решений указаны ниже

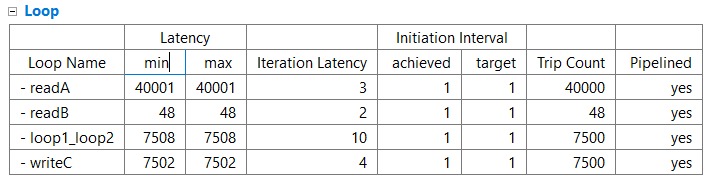

Наилучшая реализация - soln04_partition_B (подробные данные указаны ниже). Целевая тактовая частота - 333 МГц.

Наилучшая реализация - soln04_partition_B (подробные данные указаны ниже). Целевая тактовая частота - 333 МГц.

- Сведения о производительности для решения soln04_partition_B:

- Общая задержка – 55084 тактов

- Это позволит сделать вывод о том, удастся ли выполнить требование PRI <200 мс

- Теперь убедитесь, что все указатели, используемые в soln04_partition_B, добавлены в файл beamformer.cpp. Вы можете отредактировать файл вручную или добавить его, используя HLS, дважды нажав мышью на указатель и выбрав «Source File» вместо «Directive File».

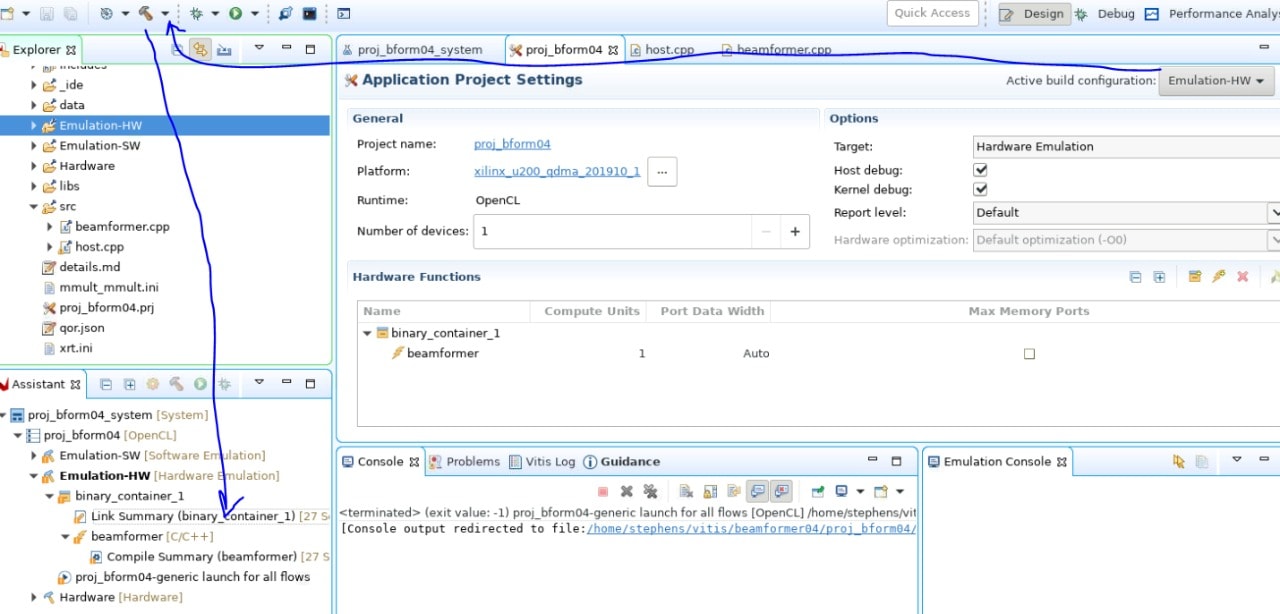

Шаг 5 – Проверка производительности с использованием HW-Emulation

- Вернитесь к проекту Vitis и замените файл «beamformer.cpp» на файл, созданный в Шаге 4 (он содержит все указатели производительности).

5.1. Выберите режим Emulation-HW и запустите на выполнение

5.2. Когда Emulation-HW завершит работу (процесс может длиться до 2 часов), нажмите «Link Summary», чтобы просмотреть результаты.

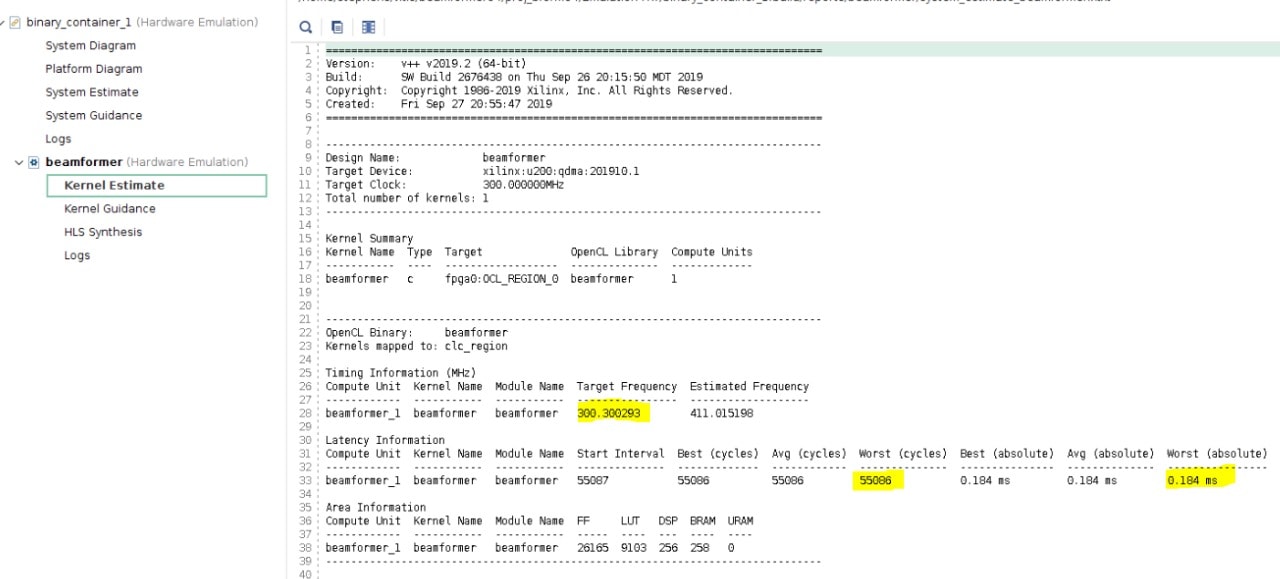

5.3. После открытия Vitis Analyzer выберите "Kernel Estimate", просмотрите данные о времени задержки и тайминги

- Задержка – 55086 тактов (частота – 300 МГц)

- Абсолютное время задержки – 184 мкс (удовлетворяет требованию «не более 200 мкс»).

Выводы

Для примера бимформинга согласно документу WP452, нам удалось достичь требуемого результата PRI (согласно спецификации – PRI<200 мкс) с применением среды Vitis для ускоренных расчетов матрицы бимформинга. Проект Vitis предусматривает использование платы Alveo U200.

Чтобы получить наилучшие значения задержек, был использован высокоуровневый синтез (HLS), управляемый прагмами, при этом мы убедились в том, что прагма II=1 играет ключевую роль. Благодаря использованию HLS удалось быстро провести тестирование вариантов реализации и получить результаты спустя всего 1-2 минуты, в то время как тестирование на эмуляторе занимает до 2х часов.

Оригинал статьи на сайте Xilinx.

Исходные коды и файлы (скачать)

Перевод: ГК Макро Групп - официальным дистрибьютором ПЛИС Xilinx.

Редактор: Викулин Владимир, инженер по применению Xilinx.

Любые вопросы по продукции Xilinx напишите нам через форму «Задать вопрос» или по телефону 8 (800) 333-06-05.